Transmit operation interface signals, Transmit datapath interface signals – Altera IP Compiler for PCI Express User Manual

Page 330

B–12

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Transmit Operation Interface Signals

The transmit interface is established per initialized virtual channel and is based on

two independent buses, one for the descriptor phase (tx_desc[127:0]) and one for

the data phase (tx_data[63:0]). Every transaction includes a descriptor. A descriptor

is a standard transaction layer packet header as defined

ion of bits 126 and 127, which indicate the

transaction layer packet group as described in the following section. Only transaction

layer packets with a normal data payload include one or more data phases.

Transmit Datapath Interface Signals

The IP core assumes that transaction layer packets sent by the application layer are

well-formed; the IP core does not detect malformed transaction layer packets sent by

the application layer.

Transmit datapath signals can be divided into the following two groups:

■

Descriptor phase signals

■

Data phase signals

1

In the following tables, transmit interface signal names suffixed with

virtual channel

additional sets of signals, each suffixed with the corresponding virtual channel

number.

describes the standard TX descriptor phase signals.

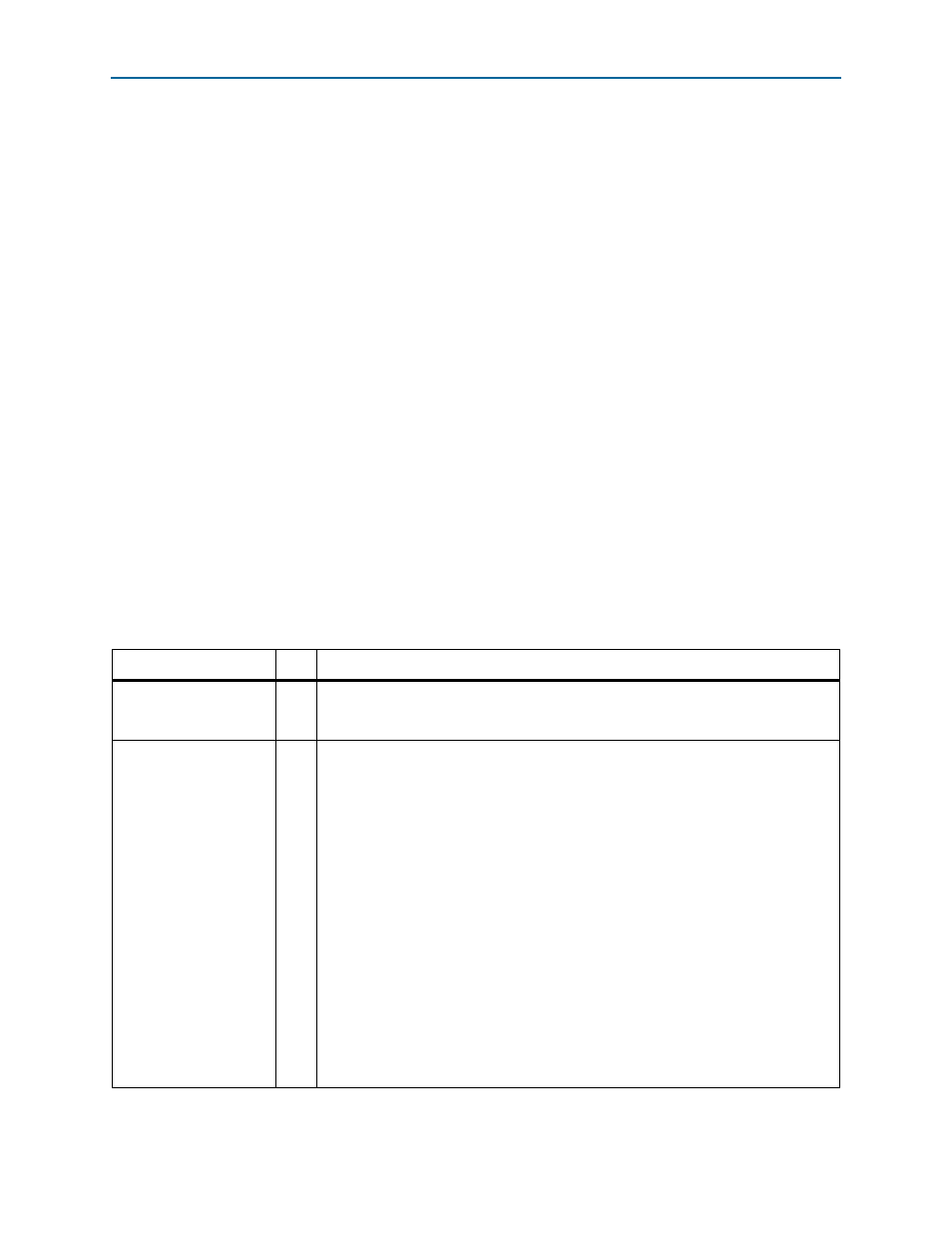

Table B–6. Standard TX Descriptor Phase Signals (Part 1 of 2)

Signal I/O

Description

tx_req

I

Transmit request. This signal must be asserted for each request. It is always asserted

with the tx_desc[127:0] and must remain asserted until tx_ack is asserted. This

signal does not need to be deasserted between back-to-back descriptor packets.

tx_desc

I

Transmit descriptor bus. The transmit descriptor bus, bits [127:0] of a transaction, can

include a 3 or 4 DWORDS PCI Express transaction header. Bits have the same meaning

as a standard transaction layer packet header as defined by the

of the header occupies bits [127:120] of

the tx_desc bus, byte 1 of the header occupies bits [119:112], and so on, with byte 15

in bits [7:0]. Refer to

Appendix A, Transaction Layer Packet (TLP) Header Formats

for

the header formats.

The following bits have special significance:

■

tx_desc[2]

or tx_desc[34] indicate the alignment of data on tx_data.

■

tx_desc[2]

(64-bit address) when 0: The first DWORD is located on

tx_data[31:0]

.

■

tx_desc[34]

(32-bit address) when 0: The first DWORD is located on bits

tx_data[31:0]

.

■

tx_desc[2]

(64-bit address) when1: The first DWORD is located on bits

tx_data[63:32]

.

■

tx_desc[34]

(32-bit address) when 1: The first DWORD is located on bits

tx_data[63:32]

.