Completion side band signals – Altera IP Compiler for PCI Express User Manual

Page 127

Chapter 5: IP Core Interfaces

5–41

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

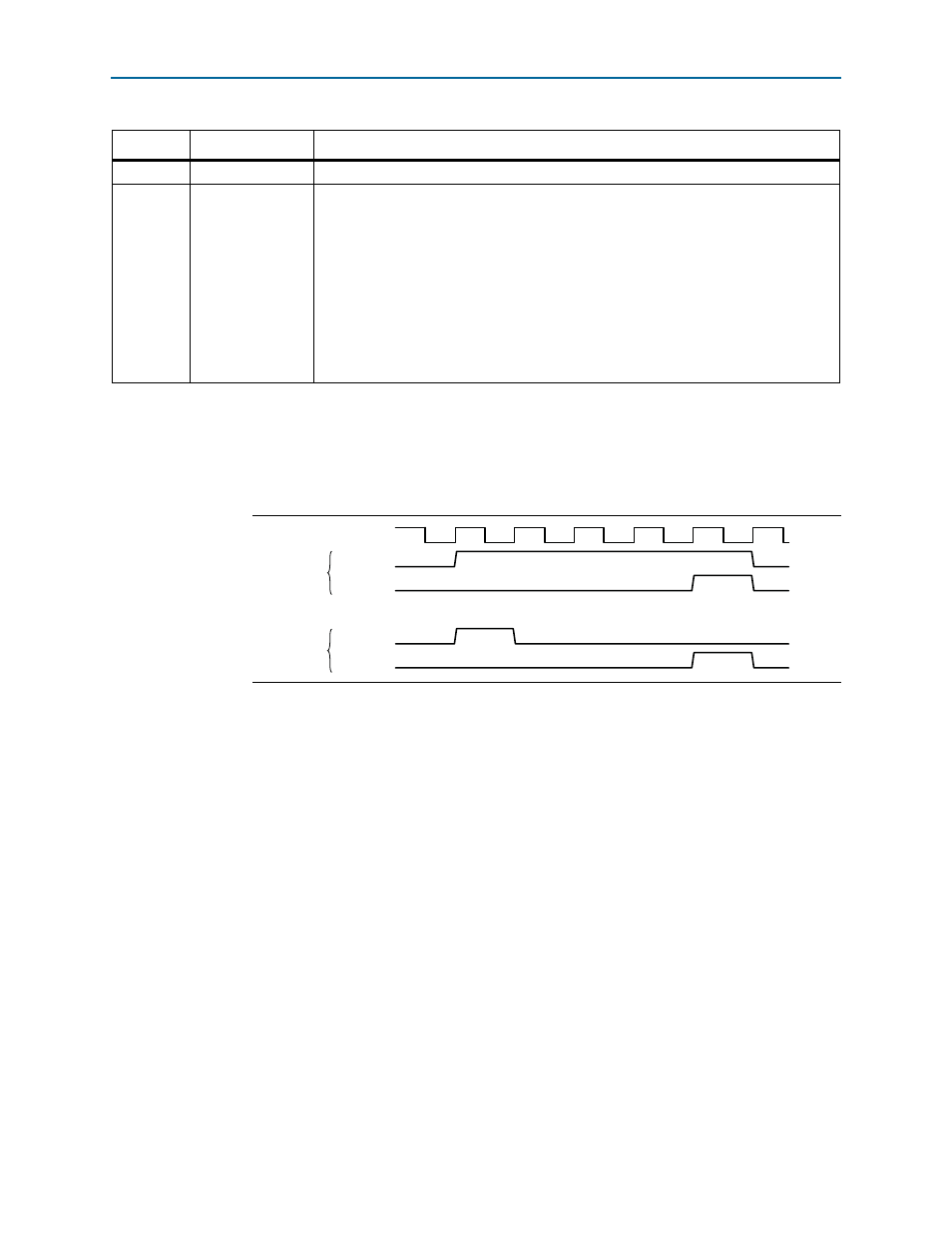

illustrates the behavior of pme_to_sr and pme_to_cr in an endpoint. First,

the IP core receives the PME_turn_off message which causes pme_to_sr to assert.

Then, the application sends the PME_to_ack message to the root port by asserting

pme_to_cr

.

Completion Side Band Signals

describes the signals that comprise the completion side band signals for the

Avalon-ST interface. The IP core provides a completion error interface that the

application can use to report errors, such as programming model errors, to it. When

the application detects an error, it can assert the appropriate cpl_err bit to indicate to

the IP core what kind of error to log. If separate requests result in two errors, both are

logged. For example, if a completer abort and a completion timeout occur, cpl_err[2]

and cpl_err[0] are both asserted for one cycle. The IP core sets the appropriate status

bits for the error in the configuration space, and automatically sends error messages

in accordance with the

PCI Express Base Specification

.

The application is responsible for sending the completion with the appropriate

completion status value for non-posted requests. Refer to

for information about errors that are automatically detected and handled by the IP

core.

[7:2]

reserved

—

[1:0]

PM_state

Specifies the power management state of the operating condition being described.

Defined encodings are:

■

2b’00 D0

■

2b’01 D1

■

2b’10 D2

■

2b’11 D

A device returns 2b’11 in this field and Aux or PME Aux in the type register to specify the

D3-Cold PM state. An encoding of 2b’11 along with any other type register value

specifies the D3-Hot state.

Table 5–20. Power Management Capabilities Register Field Descriptions (Part 2 of 2)

Bits

Field

Description

Figure 5–35. pme_to_sr and pme_to_cr in an Endpoint IP core

clk

pme_to_sr

pme_to_cr

pme_to_sr

pme_to_cr

soft

IP

hard

IP