Altera IP Compiler for PCI Express User Manual

Page 25

Chapter 2: Getting Started

2–9

Parameterizing the IP Compiler for PCI Express

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

6. Click the Buffer Setup tab to specify settings on the Buffer Setup page.

1

For the PCI Express hard IP implementation, the RX Buffer Space Allocation is fixed

at Maximum performance. This setting determines the values for a read-only table

that lists the number of posted header credits, posted data credits, non-posted header

credits, completion header credits, completion data credits, total header credits, and

total RX buffer space.

7. Specify the following power management settings.

8. On the EDA tab, turn on Generate simulation model to generate an IP functional

simulation model for the IP core. An IP functional simulation model is a

cycle-accurate VHDL or Verilog HDL model produced by the Quartus II software.

c

Use the simulation models only for simulation and not for synthesis or any

other purposes. Using these models for synthesis creates a non-functional

design.

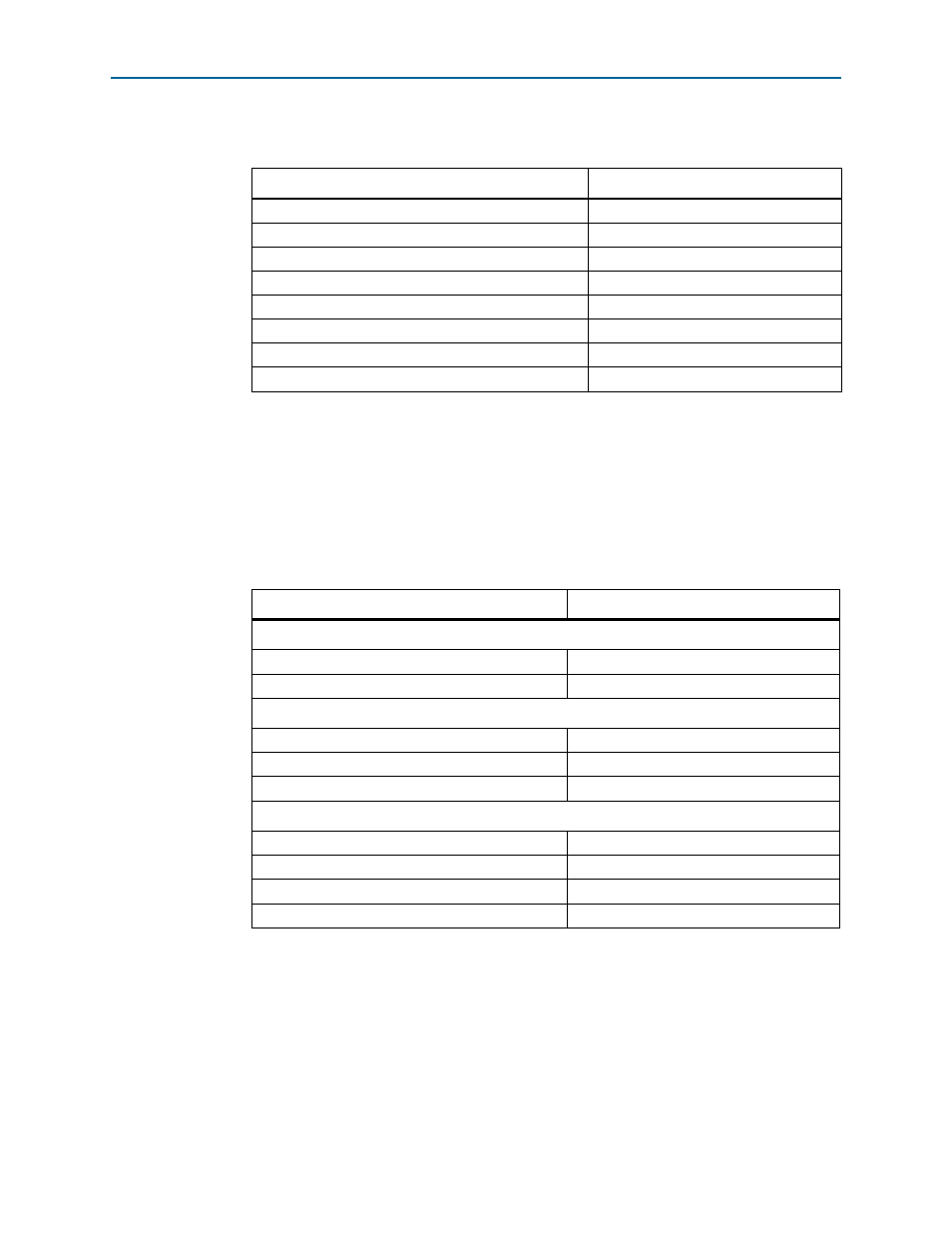

Table 2–6. Buffer Setup Parameters

Parameter

Value

Maximum payload size

512 bytes

Number of virtual channels

1

Number of low-priority VCs

None

Auto configure retry buffer size

On

Retry buffer size

16 KBytes

Maximum retry packets

64

Desired performance for received requests

Maximum

Desired performance for received completions

Maximum

Table 2–7. Power Management Parameters

Parameter

Value

L0s Active State Power Management (ASPM)

Idle threshold for L0s entry

8,192 ns

Endpoint L0s acceptable latency

< 64 ns

Number of fast training sequences (N_FTS)

Common clock

Gen2: 255

Separate clock

Gen2: 255

Electrical idle exit (EIE) before FTS

4

L1s Active State Power Management (ASPM)

Enable L1 ASPM

Off

Endpoint L1 acceptable latency

< 1 µs

L1 Exit Latency Common clock

> 64 µs

L1 Exit Latency Separate clock

> 64 µs