Table 1–9 – Altera IP Compiler for PCI Express User Manual

Page 14

1–12

Chapter 1: Datasheet

Recommended Speed Grades

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

f

Refer to “Setting Up and Running Analysis and Synthesis” in Quartus II Help and

in volume 2 of the Quartus II Handbook for more

information about how to effect this setting.

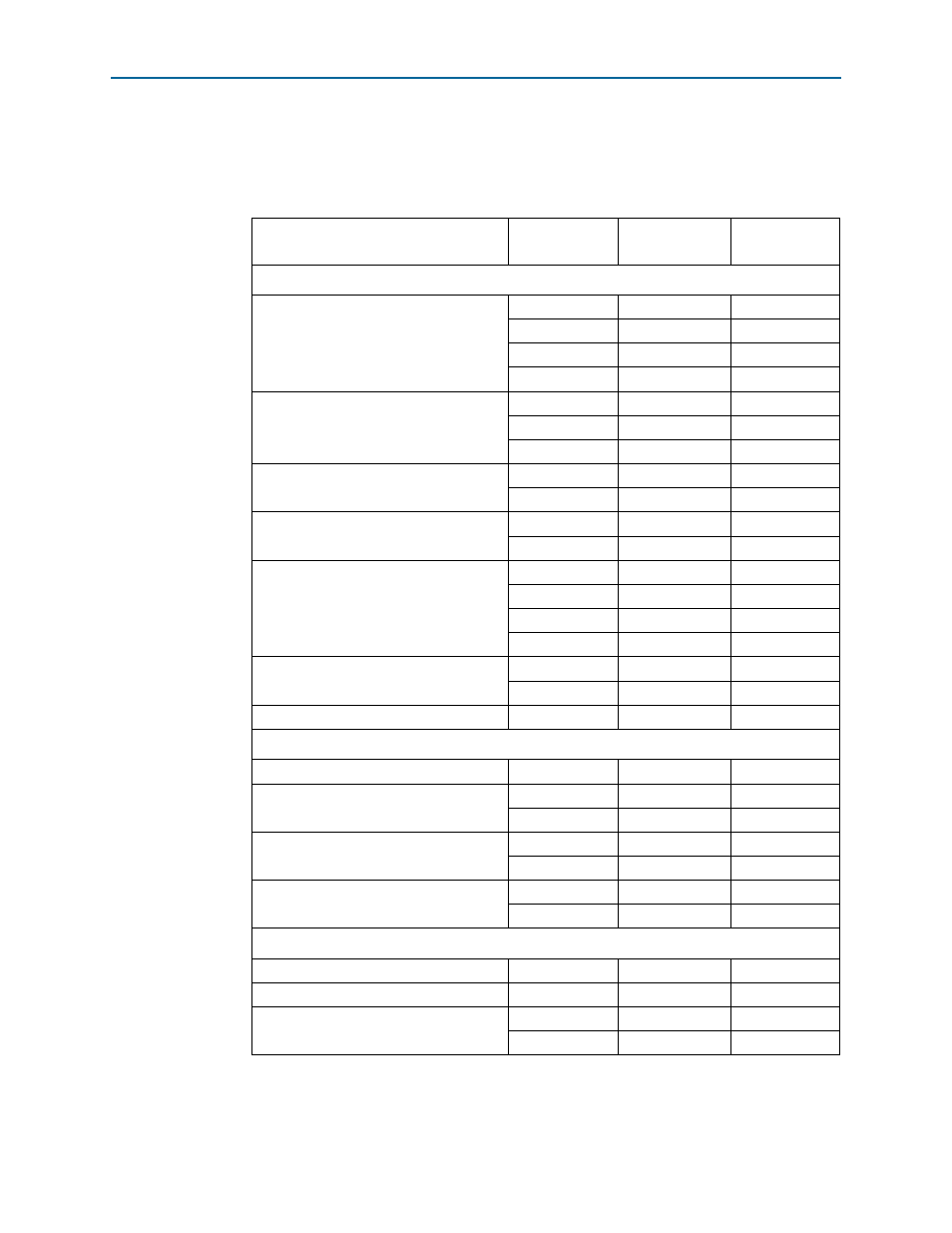

Table 1–9. Recommended Device Family Speed Grades (Part 1 of 2)

Device Family

Link Width

Internal Clock

Frequency (MHz)

Recommended

Speed Grades

Avalon-ST Hard IP Implementation

Arria II GX Gen1 with ECC Support

×1

62.5

–4,–5,–6

×1

125

–4,–5,–6

×4

125

–4,–5,–6

×8

125

–4,–5,–6

Arria II GZ Gen1 with ECC Support

×1

125

-3, -4

×4

125

-3, -4

×8

125

-3, -4

Arria II GZ Gen 2 with ECC Support

×1

125

-3

×4

125

-3

Cyclone IV GX Gen1 with ECC Support

×1

62.5

all speed grades

×1, ×2, ×4

125

all speed grades

Stratix IV GX Gen1 with ECC Support

×1

62.5

×1

125

–2, –3, –4

×4

125

–2, –3, –4

×8

250

–2, –3, –4

Stratix IV GX Gen2 with ECC Support

×1

125

×4

250

Stratix IV GX Gen2 without ECC Support

×8

500

Avalon–MM Interface–Qsys Flow

Arria II GX

×1, ×4

125

–6

Cyclone IV GX

×1, ×2, ×4

125

–6, –7

×1

62.5

–6, –7, –8

Stratix IV GX Gen1

×1, ×4

125

–2, –3, –4

×8

250

–2, –3

Stratix IV GX Gen2

×1

125

–2, –3

×4

250

–2, –3

Avalon-ST or Descriptor/Data Interface Soft IP Implementation

Arria II GX

×1, ×4

125

–4. –5

Cyclone IV GX

×1

125

Stratix IV E Gen1

×1

62.5

all speed grades

×1, ×4

125

all speed grades