Data link layer – Altera IP Compiler for PCI Express User Manual

Page 70

4–12

Chapter 4: IP Core Architecture

Data Link Layer

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

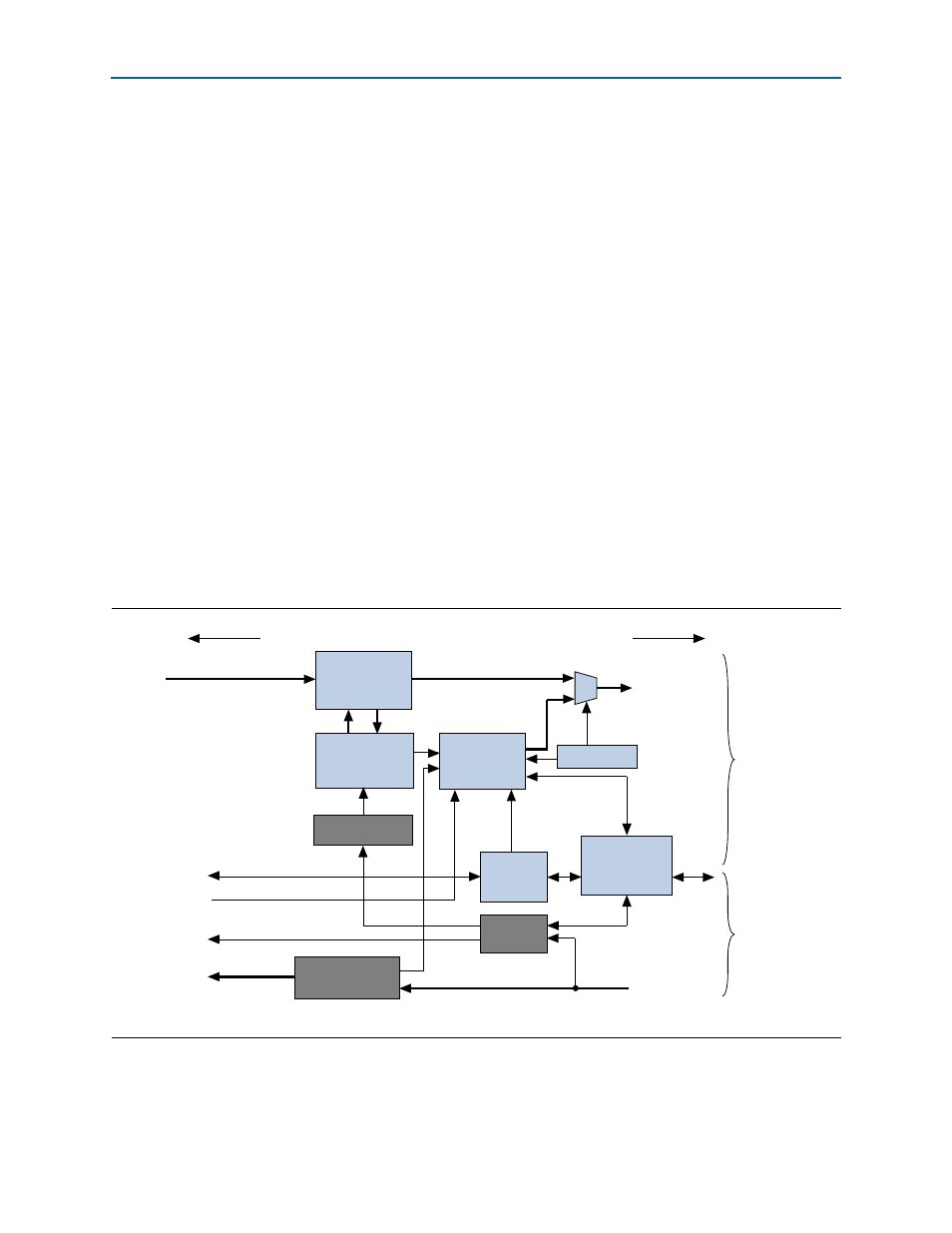

Data Link Layer

The data link layer is located between the transaction layer and the physical layer. It is

responsible for maintaining packet integrity and for communication (by data link

layer packet transmission) at the PCI Express link level (as opposed to component

communication by transaction layer packet transmission in the interconnect fabric).

The data link layer is responsible for the following functions:

■

Link management through the reception and transmission of data link layer

packets, which are used for the following functions:

■

To initialize and update flow control credits for each virtual channel

■

For power management of data link layer packet reception and transmission

■

To transmit and receive ACK/NACK packets

■

Data integrity through generation and checking of CRCs for transaction layer

packets and data link layer packets

■

Transaction layer packet retransmission in case of NAK data link layer packet

reception using the retry buffer

■

Management of the retry buffer

■

Link retraining requests in case of error through the LTSSM of the physical layer

illustrates the architecture of the data link layer.

Figure 4–8. Data Link Layer

To Transaction Layer

Tx Transaction Layer

Packet Description & Data

Transaction Layer

Packet Generator

Retry Buffer

To Physical Layer

Tx Packets

Ack/Nack

Packets

Receive

Data Path

Transmit

Data Path

Rx Packets

DLLP

Checker

Transaction Layer

Packet Checker

DLLP

Generator

Tx Arbitration

Data Link Control

& Management

State Machine

Control

& Status

Configuration Space

Tx Flow Control Credits

Rx Flow Control Credits

Rx Transation Layer

Packet Description & Data

Power

Management

Function