Parameterizing the ip compiler for pci express – Altera IP Compiler for PCI Express User Manual

Page 23

Chapter 2: Getting Started

2–7

Parameterizing the IP Compiler for PCI Express

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Parameterizing the IP Compiler for PCI Express

This section guides you through the process of parameterizing the IP Compiler for

PCI Express as an endpoint, using the same options that are chosen in

. Complete the following steps to specify the

parameters:

1. In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP

core to customize. The parameter editor appears.

2. Specify a top-level name for your custom IP variation. This name identifies the IP

core variation files in your project. For this walkthrough, specify top.v for the

name of the IP core file:

3. Specify the following values in the parameter editor:

4. To enable all of the tests in the provided testbench and chaining DMA example

design, make the base address register (BAR) assignments. Bar2 or Bar3 is

required.

. provides the BAR assignments in tabular format.

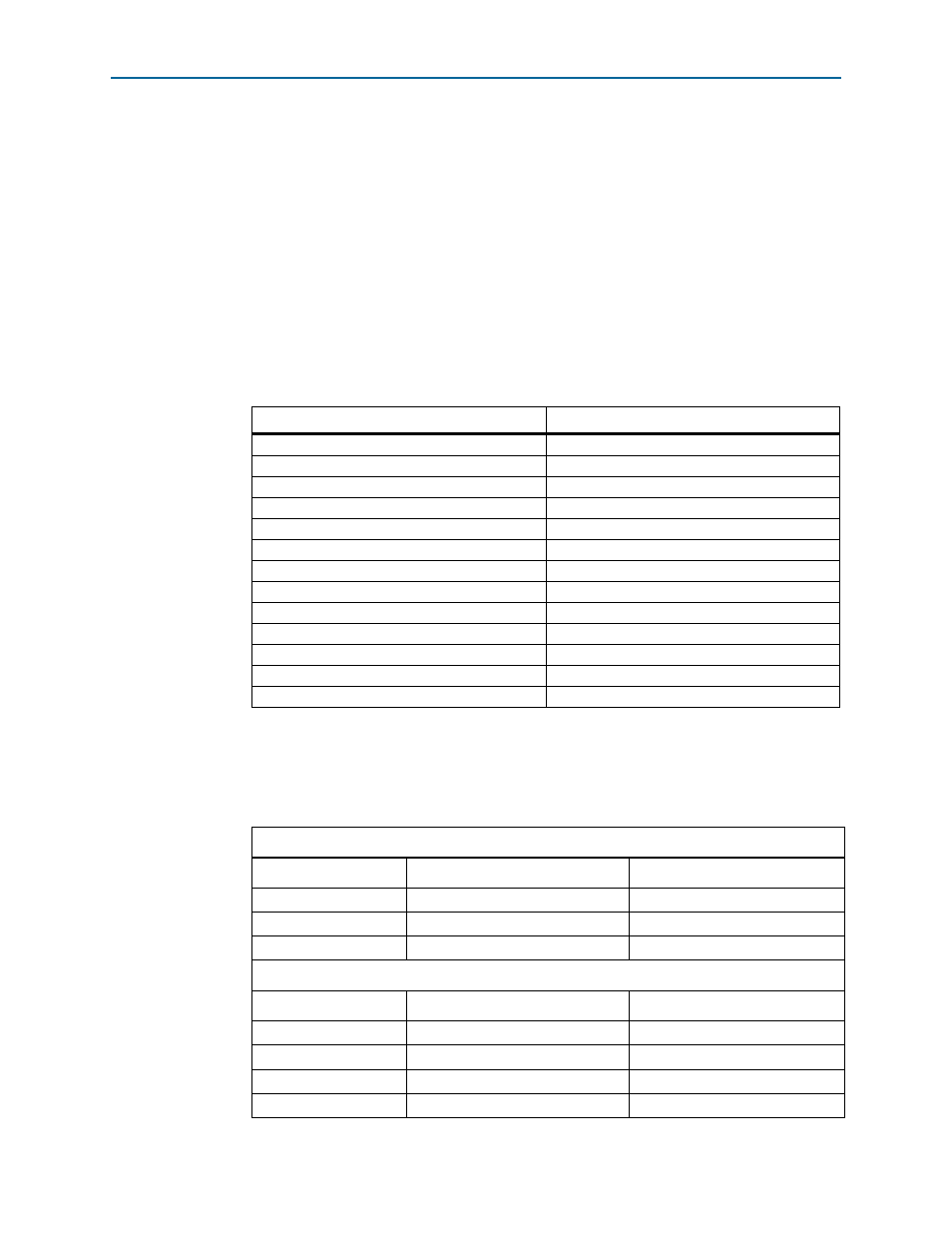

Table 2–3. System Settings Parameters

Parameter

Value

PCIe Core Type

PCI Express hard IP

PHY type

Stratix IV GX

PHY interface

serial

Configure transceiver block

Use default settings.

Lanes

×8

Xcvr ref_clk

100 MHz

Application interface

Avalon-ST 128 -bit

Port type

Native Endpoint

PCI Express version

2.0

Application clock

250 MHz

Max rate

Gen 2 (5.0 Gbps)

Test out width

64 bits

HIP reconfig

Disable

Table 2–4. PCI Registers (Part 1 of 2)

PCI Base Registers (Type 0 Configuration Space)

BAR

BAR TYPE

BAR Size

0

32-Bit Non-Prefetchable Memory

256 MBytes - 28 bits

1

32-Bit Non-Prefetchable Memory

256 KBytes - 18 bits

2

32-bit Non-Prefetchable Memory

256 KBytes -18 bits

PCI Read-Only Registers

Register Name

Value

Device ID

0xE001

Subsystem ID

0x2801

Revision ID

0x01

Vendor ID

0x1172