Altera IP Compiler for PCI Express User Manual

Page 201

Chapter 11: Flow Control

11–5

Throughput of Non-Posted Reads

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Nevertheless, maintaining maximum throughput of completion data packets is

important. PCI Express endpoints must offer an infinite number of completion

credits. The IP Compiler for PCI Express must buffer this data in the RX buffer until

the application can process it. Because the IP Compiler for PCI Express is no longer

managing the RX buffer through the flow control mechanism, the application must

manage the RX buffer by the rate at which it issues read requests.

To determine the appropriate settings for the amount of space to reserve for

completions in the RX buffer, you must make an assumption about the length of time

until read completions are returned. This assumption can be estimated in terms of an

additional delay, beyond the FC Update Loop Delay, as discussed in the section

“Throughput of Posted Writes” on page 11–1

. The paths for the read requests and the

completions are not exactly the same as those for the posted writes and FC Updates in

the IP Compiler for PCI Express logic. However, the delay differences are probably

small compared with the inaccuracy in the estimate of the external read to completion

delays.

Assuming there is a PCI Express switch in the path between the read requester and

the read completer and assuming typical read completion times for root ports,

shows the estimated completion space required to cover the read

transaction’s round trip delay.

1

Note also that the completions can be broken up into multiple completions of smaller

packet size.

With multiple completions, the number of available credits for completion headers

must be larger than the completion data space divided by the maximum packet size.

Instead, the credit space for headers must be the completion data space (in bytes)

divided by 64, because this is the smallest possible read completion boundary. Setting

the Desired performance for received completions to High on the Buffer Setup page

when specifying parameter settings in your IP core configures the RX buffer with

enough space to meet the above requirements. You can adjust the Desired

performance

for received completions up or down from the High setting to tailor the

RX buffer size to your delays and required performance.

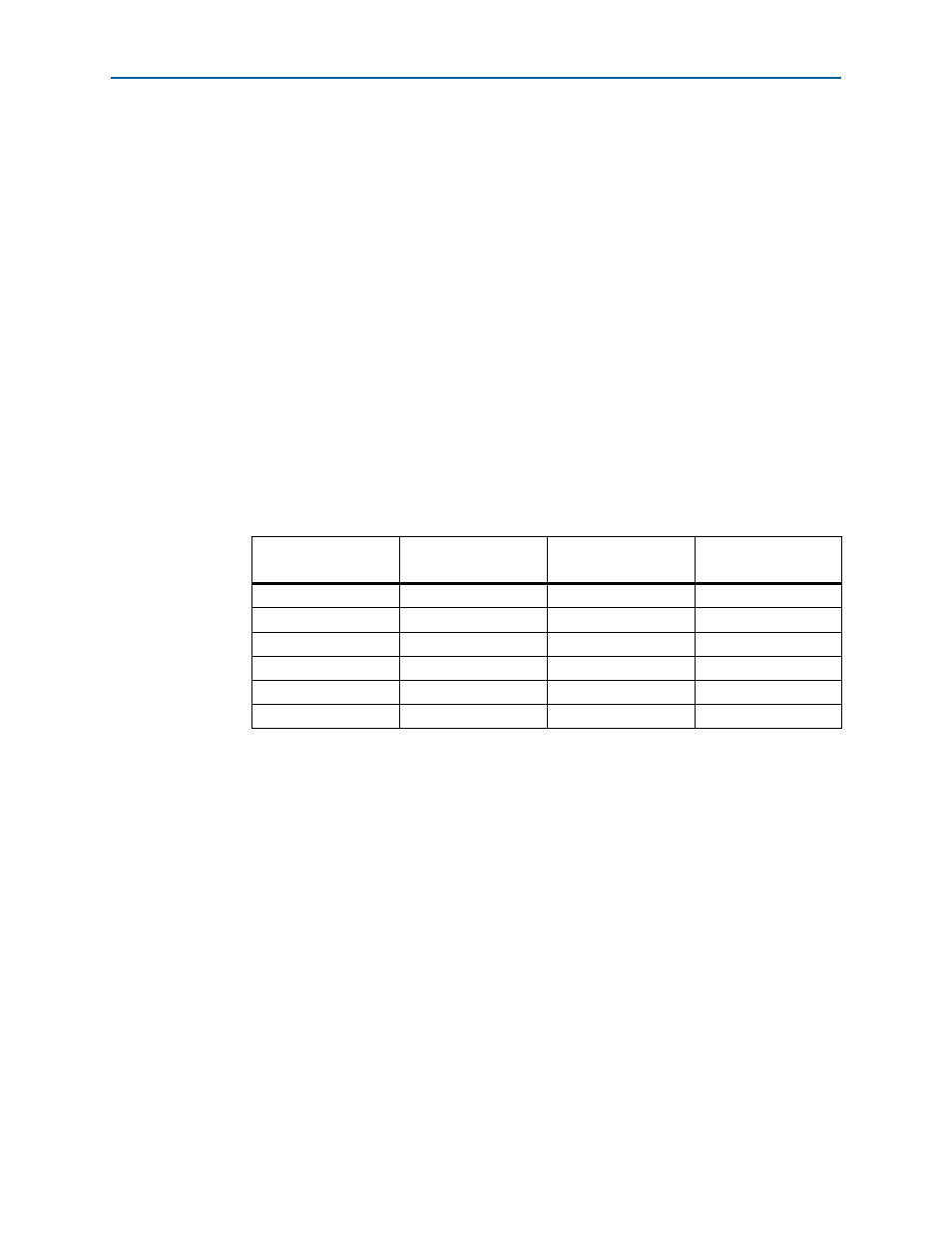

Table 11–3. Completion Data Space (in Credit units) to Cover Read Round Trip Delay

Max Packet Size

×8 Function

Typical

×4 Function

Typical

×1 Function

Typical

128

120

96

56

256

144

112

80

512

192

160

128

1024

256

256

192

2048

384

384

384

4096

768

768

768