Active state power management (aspm), Tx path, Note 1) – Altera IP Compiler for PCI Express User Manual

Page 185

Chapter 9: Optional Features

9–3

Active State Power Management (ASPM)

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Active State Power Management (ASPM)

The PCI Express protocol mandates link power conservation, even if a device has not

been placed in a low power state by software. ASPM is initiated by software but is

subsequently handled by hardware. The IP core automatically shifts to one of two low

power states to conserve power:

■

L0s ASPM—The PCI Express protocol specifies the automatic transition to L0s. In

this state, the IP core transmits electrical idle but can maintain an active reception

interface because only one component across a link moves to a lower power state.

Main power and reference clocks are maintained.

1

L0s ASPM can be optionally enabled when using the Arria GX,

Cyclone IV GX, HardCopy IV GX, Stratix II GX, or Stratix IV GX internal

PHY. It is supported for other device families to the extent allowed by the

attached external PHY device.

■

L1 ASPM—Transition to L1 is optional and conserves even more power than L0s.

In this state, both sides of a link power down together, so that neither side can

send or receive without first transitioning back to L0.

1

L1 ASPM is not supported when using the Arria GX, Cyclone IV GX,

HardCopy IV GX, Stratix II GX, or Stratix IV GX internal PHY. It is

supported for other device families to the extent allowed by the attached

external PHY device.

An endpoint can assert the pm_pme signal to initiate a power_management_event

message which is sent to the root complex. If the IP core is in the L0s or L1 state, the

link exits the low-power state to send this message. The pm_pme signal is edge-

senstive. If the link is in the L2 state, a Beacon (or Wake#) is generated to reinitialize the

link before the core can generate the power_management_event message. Wake# is

hardwired to 0 for root ports.

How quickly a component powers up from a low-power state, and even whether a

component has the right to transition to a low power state in the first place, depends

on

,

register,

, recorded in the

register, and ASPM Control in the

register.

Yes

No

TD

=0, without ECRC

TD

=0, without ECRC

Core forwards the

ECRC

TD

=1, with ECRC

TD

=1, with ECRC

Yes

TD

=0, without ECRC

TD

=0, without ECRC

TD

=1, with ECRC

TD

=1, with ECRC

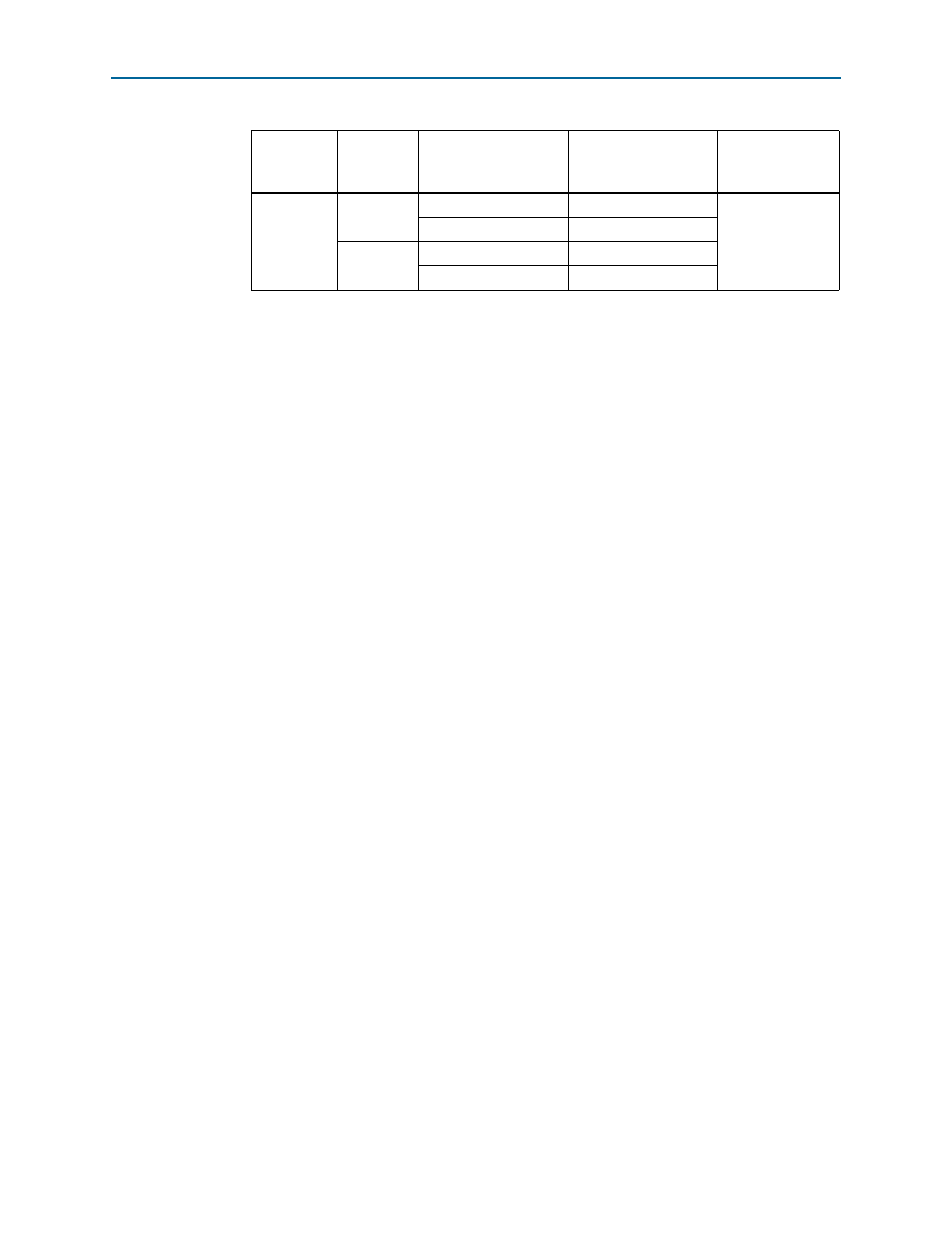

Notes to

(1) All unspecified cases are unsupported and the behavior of the IP core is unknown.

(2) The ECRC Generation Enable is in the configuration space advanced error capabilities and control register.

Table 9–2. ECRC Generation and Forwarding on TX Path

(Note 1)

ECRC

Forwarding

ECRC

Generation

Enable

(2)

TLP on Application

TLP on Link

Comments