Altera IP Compiler for PCI Express User Manual

Page 217

Chapter 13: Reconfiguration and Offset Cancellation

13–7

Dynamic Reconfiguration

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

0xA1

BAR0[31:0].

0 BAR0[0]: I/O Space.

b’0

2:1 BAR0[2:1]: Memory Space.

b’10

10: 64-bit address.

00: 32-bit address.

3 BAR0[3]: Prefetchable.

b’1

BAR0[31:4]: Bar size mask.

0xFFFFFFF

15:4 BAR0[15:4].

b’0

0xA2

15:0 BAR0[31:16].

b’0

0xA3

BAR1[63:32].

b’0

0

BAR1[32]: I/O Space.

b’0

2:1

BAR1[34:33]: Memory Space (see bit settings for

BAR0).

b’0

3

BAR1[35]: Prefetchable.

b’0

BAR1[63:36]: Bar size mask.

b’0

15:4 BAR1[47:36].

b’0

0xA4

15:0 BAR1[63:48].

b’0

0xA5

BAR2[95:64]:

b’0

0

BAR2[64]: I/O Space.

b’0

2:1

BAR2[66:65]: Memory Space (see bit settings for

BAR0).

b’0

3

BAR2[67]: Prefetchable.

b’0

BAR2[95:68]: Bar size mask.

b’0

15:4 BAR2[79:68].

b’0

0xA6

15:0 BAR2[95:80].

b’0

BAR3[127:96].

b’0

0

BAR3[96]: I/O Space.

b’0

2:1

BAR3[98:97]: Memory Space (see bit settings for

BAR0).

b’0

3

BAR3[99]: Prefetchable.

b’0

BAR3[127:100]: Bar size mask.

b’0

0xA7

15:4 BAR3[111:100].

b’0

0xA8

15:0 BAR3[127:112].

b’0

0xA9

BAR4[159:128].

b’0

0

BAR4[128]: I/O Space.

b’0

2:1

BAR4[130:129]: Memory Space (see bit settings for

BAR0).

b’0

3

BAR4[131]: Prefetchable.

b’0

BAR4[159:132]: Bar size mask.

b’0

15:4 BAR4[143:132].

b’0

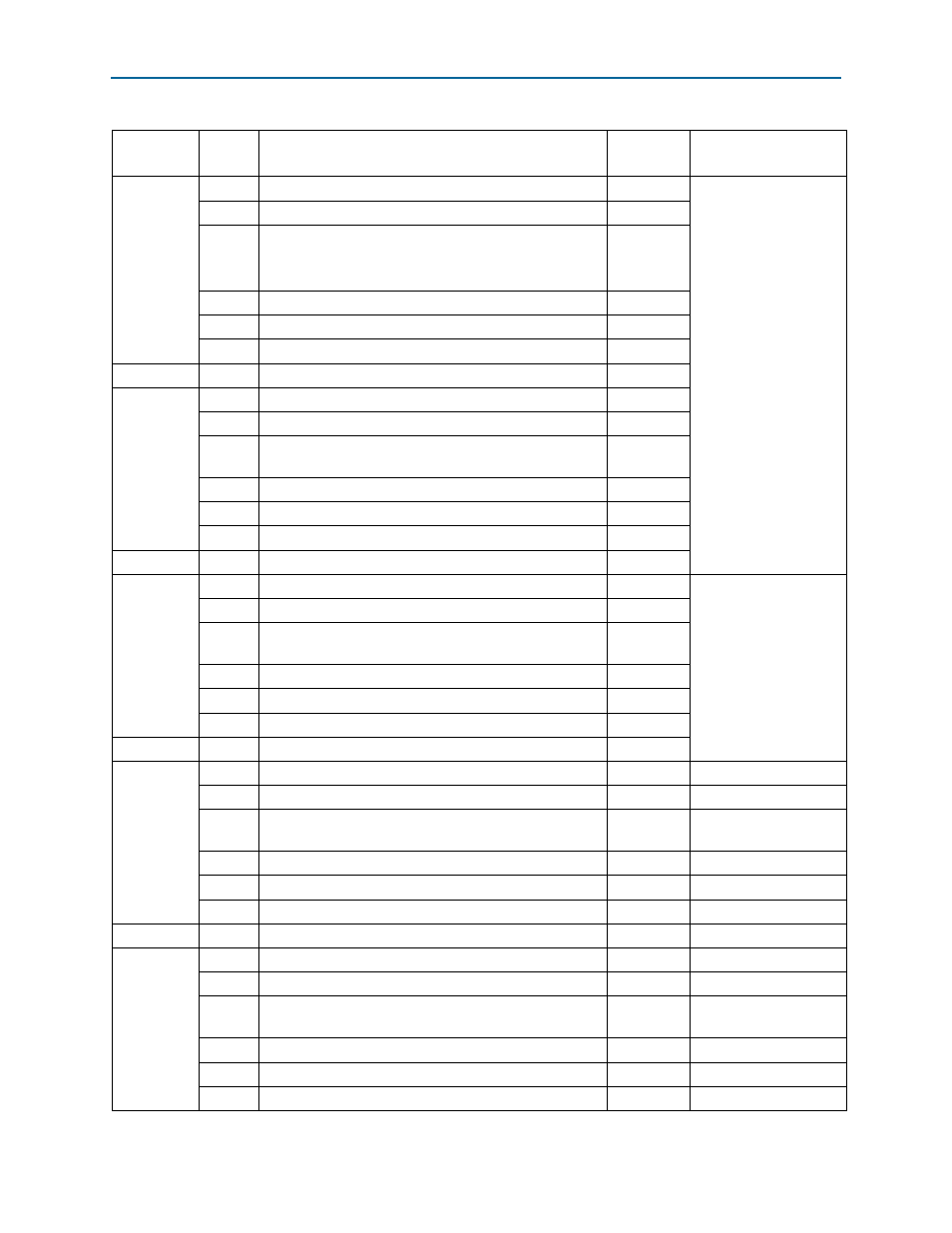

Table 13–1. Dynamically Reconfigurable Registers in the Hard IP Implementation (Part 6 of 7)

Address

Bits

Description

Default

Value

Additional Information