Avalon-mm-to-pci express address translation – Altera IP Compiler for PCI Express User Manual

Page 80

4–22

Chapter 4: IP Core Architecture

PCI Express Avalon-MM Bridge

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

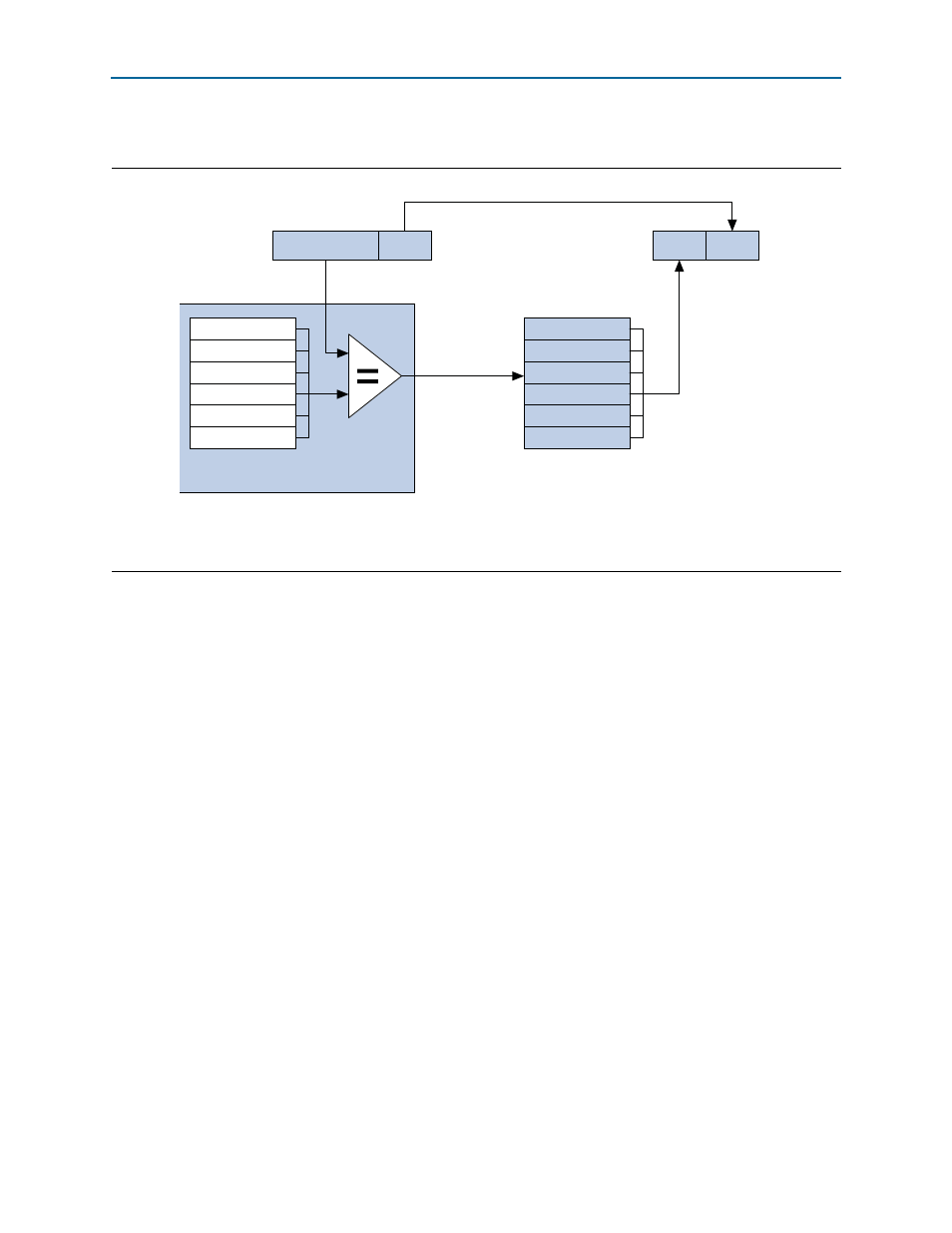

depicts the PCI Express Avalon-MM bridge address translation process.

The Avalon-MM RX master module port has an 8-byte datapath. The Qsys

interconnect fabric does not support native addressing. Instead, it supports dynamic

bus sizing. In this method, the interconnect fabric handles mismatched port widths

transparently.

f

For more information about both native addressing and dynamic bus sizing, refer to

the “Address Alignment” section in the “Avalon Memory-Mapped Interfaces”

.

Avalon-MM-to-PCI Express Address Translation

The Avalon-MM address of a received request on the TX Slave Module port is

translated to the PCI Express address before the request packet is sent to the

transaction layer. This address translation process proceeds by replacing the MSB bits

of the Avalon-MM address with the value from a specific translation table entry; the

LSB bits remain unchanged. The number of MSB bits to be replaced is calculated

based on the total address space of the upstream PCI Express devices that the IP

Compiler for PCI Express can access.

The address translation table contains up to 512 possible address translation entries

that you can configure. Each entry corresponds to a base address of the PCI Express

memory segment of a specific size. The segment size of each entry must be identical.

The total size of all the memory segments is used to determine the number of address

MSB bits to be replaced. In addition, each entry has a 2-bit field, Sp[1:0], that

Figure 4–11. PCI Express Avalon-MM Bridge Address Translation

Note to

(1) N is the number of pass-through bits (BAR specific). M is the number of Avalon-MM address bits. P is the number of PCI Express address bits

(32 or 64).

PCI Express Address

Inside IP Compiler for PCI Express

Matched BAR

selects Avalon-MM

address

Low address bits unchanged

(BAR-specific number of bits)

Hard-coded BAR-specific

Avalon-MM Addresses

Avalon-MM Address

BAR-specific Number of

High Avalon-MM Bits

Avalon Address B0

Avalon Address B1

Avalon Address B2

Avalon Address B3

Avalon Address B4

Avalon Address B5

M-1

N N-1

0

P-1

N N-1

0

High

Low

Low

High

BAR0 (or 0:1)

BAR1

BAR2

BAR3

BAR4

BAR5