Altera IP Compiler for PCI Express User Manual

Page 93

Chapter 5: IP Core Interfaces

5–7

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

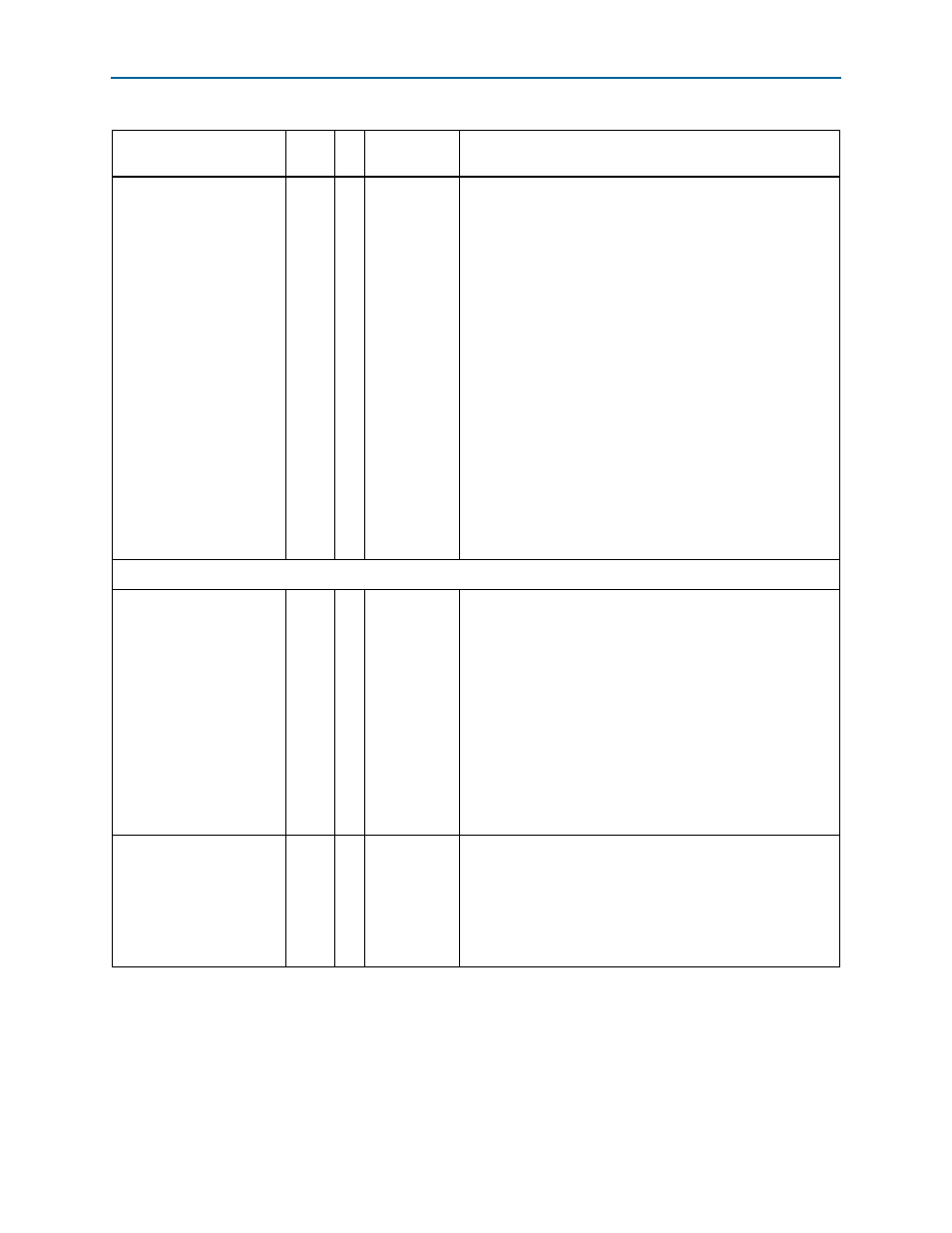

rx_st_err

1

O

error

Indicates that there is an uncorrectable error correction coding

(ECC) error in the core’s internal RX buffer of the associated VC.

This signal is only active for the hard IP implementations when

ECC is enabled. ECC is automatically enabled by the Quartus II

assembler in memory blocks, the retry buffer, and the RX buffer

for all hard IP variants with the exception of Gen2 ×8. ECC

corrects single–bit errors and detects double–bit errors on a

per byte basis.

When an uncorrectable ECC error is detected, rx_st_err is

asserted for at least 1 cycle while rx_st_valid is asserted. If

the error occurs before the end of a TLP payload, the packet

may be terminated early with an rx_st_eop and with

rx_st_valid

deasserted on the cycle after the eop.

Altera recommends resetting the IP Compiler for PCI Express

when an uncorrectable (double–bit) ECC error is detected and

the TLP cannot be terminated early. Resetting guarantees that

the Configuration Space Registers are not corrupted by an

errant packet.

This signal is not available for the hard IP implementation in

Arria II GX devices.

Component Specific Signals

rx_st_mask

1

I

component

specific

Application asserts this signal to tell the IP core to stop sending

non-posted requests. This signal does not affect non-posted

requests that have already been transferred from the

transaction layer to the Avalon-ST Adaptor module. This signal

can be asserted at any time. The total number of non-posted

requests that can be transferred to the application after

rx_st_mask

is asserted is not more than 26 for 128-bit mode

and not more than 14 for 64-bit mode.

Do not design your application layer logic so that rx_st_mask

remains asserted until certain Posted Requests or Completions

are received. To function correctly, the rx_st_mask is

eventually deasserted without waiting for posted requests or

completions.

rx_st_bardec

8

O

component

specific

The decoded BAR bits for the TLP. They correspond to the

transaction layer's rx_desc[135:128]. Valid for MRd, MWr,

IOWR

, and IORD TLPs; ignored for the CPL or message TLPs.

They are valid on the 2nd cycle of rx_st_data

datapath. For a 128-bit datapath rx_st_bardec

the first cycle.

illustrate the timing

of this signal for 64- and 128-bit data, respectively.

Table 5–2. 64- or 128-Bit Avalon-ST RX Datapath (Part 2 of 3)

Signal

Width

Dir

Avalon-ST

Type

Description