Transaction without data payload – Altera IP Compiler for PCI Express User Manual

Page 325

Chapter :

B–7

Descriptor/Data Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

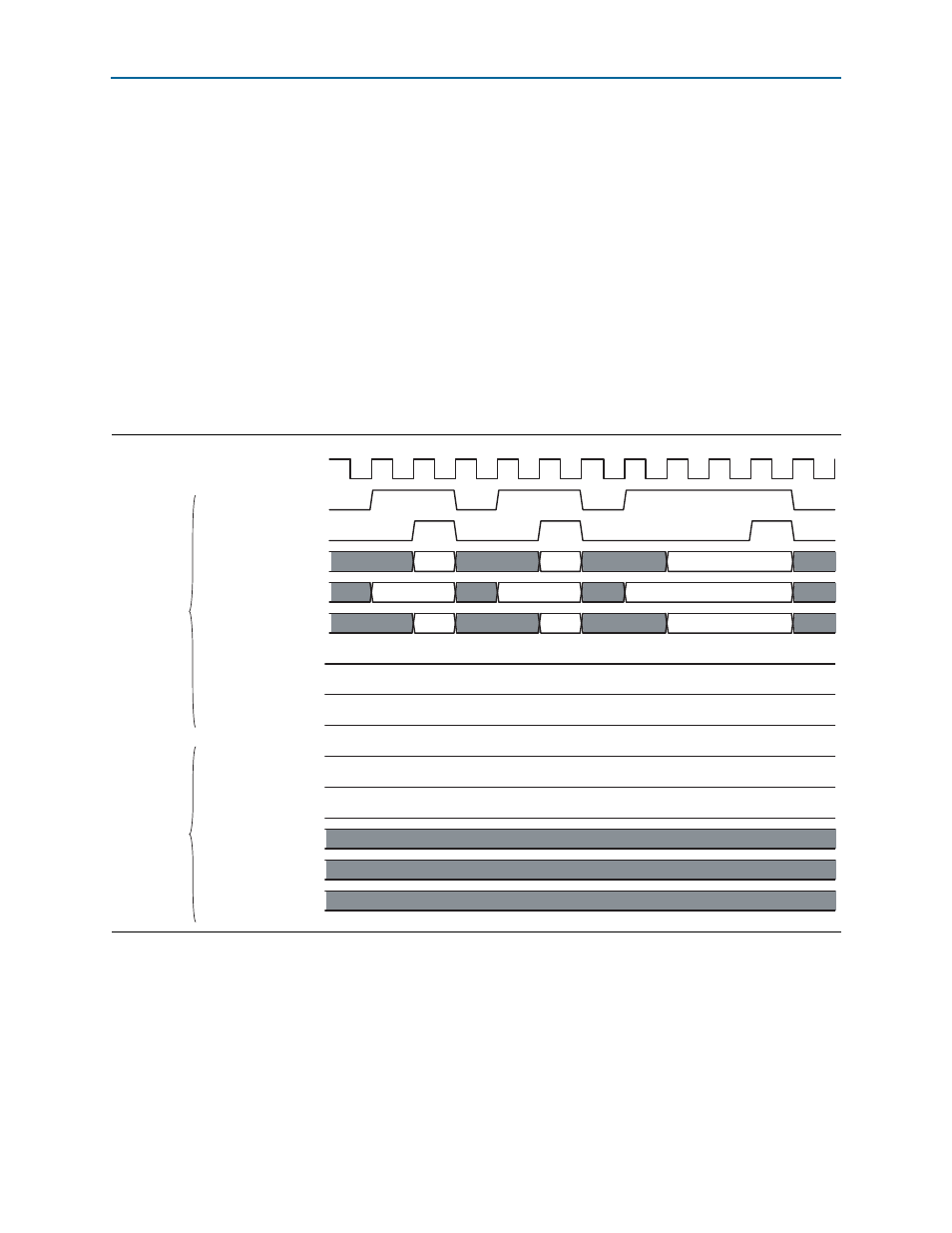

Transaction without Data Payload

In

, the IP core receives three consecutive transactions, none of which have

data payloads:

■

Memory read request (64-bit addressing mode)

■

Memory read request (32-bit addressing mode)

■

I/O read request

In clock cycles 4, 7, and 12, the IP core updates flow control credits after each

transaction layer packet has either been acknowledged or aborted. When necessary,

the IP core generates flow control DLLPs to advertise flow control credit levels.

The I/O read request initiated at clock cycle 8 is not acknowledged until clock cycle 11

with assertion of rx_ack. The relatively late acknowledgment could be due to possible

congestion.

Retried Transaction and Masked Non-Posted Transactions

When the application layer can no longer accept non-posted requests, one of two

things happen: either the application layer requests the packet be resent or it asserts

rx_mask

. For the duration of rx_mask, the IP core masks all non-posted transactions

and reprioritizes waiting transactions in favor of posted and completion transactions.

When the application layer can once again accept non-posted transactions, rx_mask is

deasserted and priority is given to all non-posted transactions that have accumulated

in the receive buffer.

Figure B–5. RX Three Transactions without Data Payloads Waveform

clk

rx_req

rx_ack

rx_desc[135:128]

rx_desc[127:64]

rx_desc[63:0]

rx_abort

rx_retry

rx_mask

rx_dfr

rx_dv

rx_ws

rx_data[63:32]

rx_data[31:0]

rx_be[7:0]

valid

valid

valid

MEMRD64

MEMRD32

I/O RD

valid

valid

valid

1

2

3

4

5

6

7

8

9

10

11

12

Descriptor

Signals

Data

Signals