Altera IP Compiler for PCI Express User Manual

Page 326

B–8

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Each virtual channel has a dedicated datapath and associated buffers and no ordering

relationships exist between virtual channels. While one virtual channel may be

temporarily blocked, data flow continues across other virtual channels without

impact. Within a virtual channel, reordering is mandatory only for non-posted

transactions to prevent deadlock. Reordering is not implemented in the following

cases:

■

Between traffic classes mapped in the same virtual channel

■

Between posted and completion transactions

■

Between transactions of the same type regardless of the relaxed-ordering bit of

the transaction layer packet

In

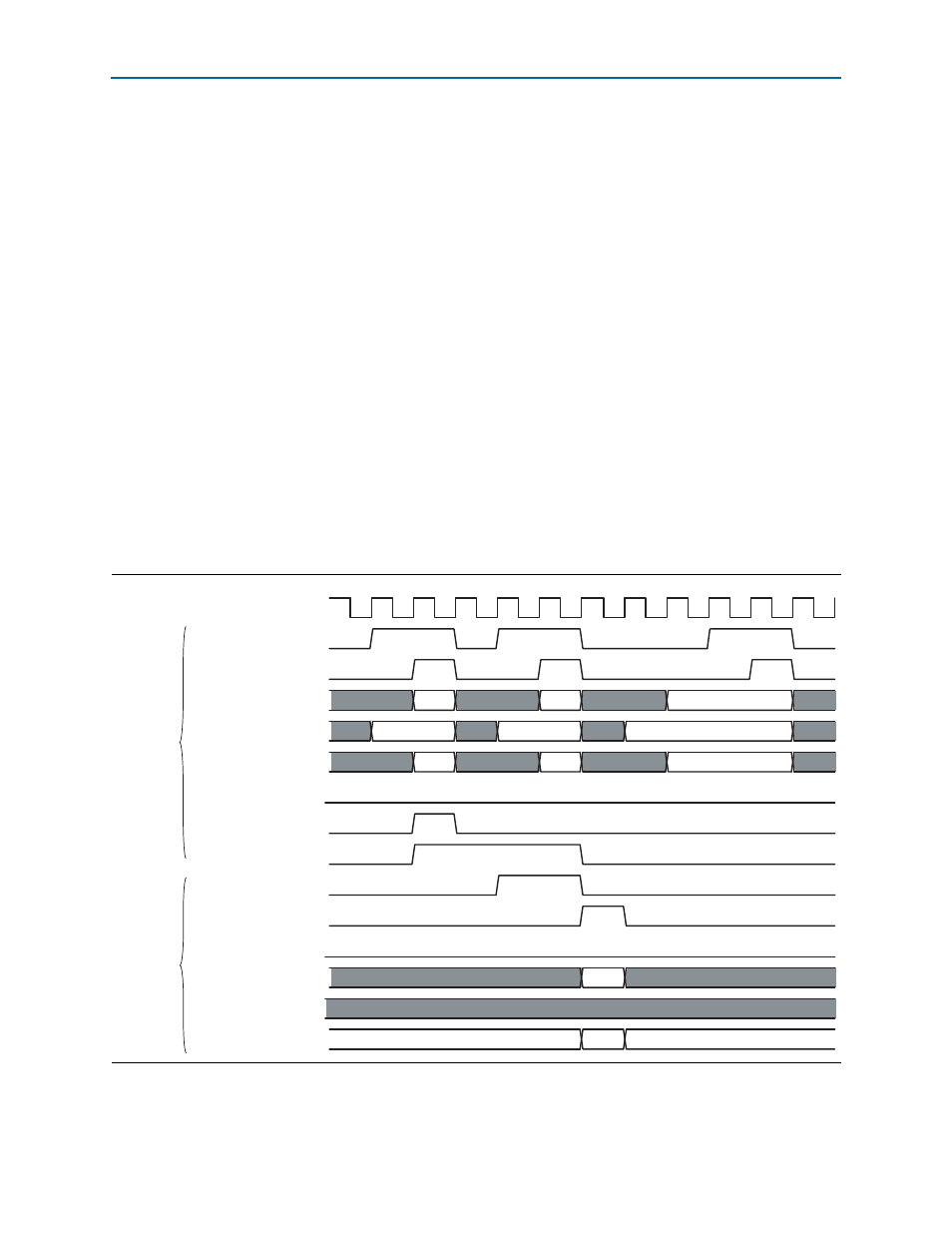

, the IP core receives a memory read request transaction of 4 DWORDS

that it cannot immediately accept. A second transaction (memory write transaction of

one DWORD) is waiting in the receive buffer. Bit 2 of rx_data[63:0] for the memory

write request is set to 1.

In clock cycle three, transmission of non-posted transactions is not permitted for as

long as rx_mask is asserted.

Flow control credits are updated only after a transaction layer packet has been

extracted from the receive buffer and both the descriptor phase and data phase (if

any) have ended. This update happens in clock cycles 8 and 12 in

.

Figure B–6. RX Retried Transaction and Masked Non-Posted Transaction Waveform

clk

rx_req

rx_ack

rx_desc[135:128]

rx_desc[127:64]

rx_desc[63:0]

rx_abort

rx_retry

rx_mask

rx_dfr

rx_dv

rx_ws

rx_data[63:32]

rx_data[31:0]

rx_be[7:0]

valid

valid

valid

MEMRD 4 DW

MEMWR 1DW

MEMRD 4DW

valid

valid

valid

DW 0

0x00

0xF0

0x00

1

2

3

4

5

6

7

8

9

10

11

12

Descriptor

Signals

Data

Signals