0x08c, 0x084, 0x090 – Altera IP Compiler for PCI Express User Manual

Page 152: 0x094, 0x068, Table 6–5, Table 6–6, For details.), Table 6–7

6–4

Chapter 6: Register Descriptions

Configuration Space Register Content

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

describes the MSI-X capability structure.

describes the power management capability structure.

describes the PCI Express capability structure for specification versions 1.0a

and 1.1.

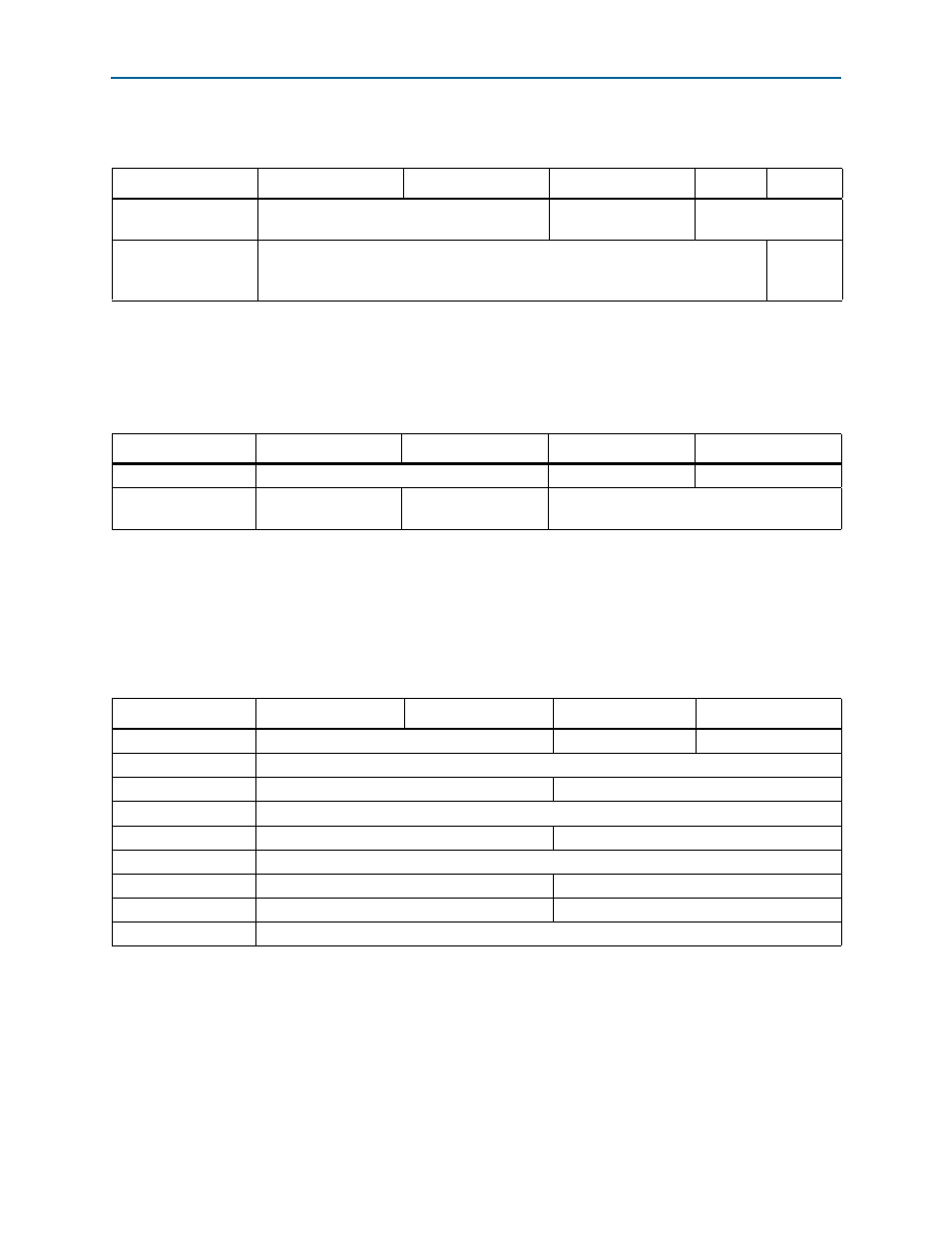

Table 6–5. MSI-X Capability Structure, Rev2 Spec: MSI and MSI-X Capability Structures

Byte Offset

31:24

23:16

15:8

7:3

2:0

0x068

Message Control

[26:16]

Next Cap Ptr

Capability ID

0x06C

MSI-X Table Offset

Note to

for a comprehensive list of correspondences between the configuration space registers and the

Table 6–6. Power Management Capability Structure, Rev2 Spec: Power Management Capability Structure

Byte Offset

31:24

23:16

15:8

7:0

0x078

Capabilities Register

Next Cap PTR

Cap ID

0x07C

Data

PM Control/Status

Bridge Extensions

Power Management Status & Control

Note to

(1) Refer to

for a comprehensive list of correspondences between the configuration space registers

Table 6–7. PCI Express Capability Structure Version 1.0a and 1.1

, Rev2 Spec: PCI Express Capabilities

Register and PCI Express Capability List Register

Byte Offset

31:24

23:16

15:8

7:0

0x080

PCI Express Capabilities Register

Next Cap Pointer

PCI Express Cap ID

0x084

0x088

Device Status

Device Control

0x08C

0x090

Link Status

Link Control

0x094

0x098

Slot Status

Slot Control

0x09C

Reserved

Root Control

0x0A0

Root Status

Note to

(1) Reserved and preserved. As per the PCI Express Base Specification 1.1, this register is reserved for future RW implementations. Registers are

read-only and must return 0 when read. Software must preserve the value read for writes to bits.

(2) Refer to

for a comprehensive list of correspondences between the configuration space registers