Transaction aborted, Transaction with data payload – Altera IP Compiler for PCI Express User Manual

Page 327

Chapter :

B–9

Descriptor/Data Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

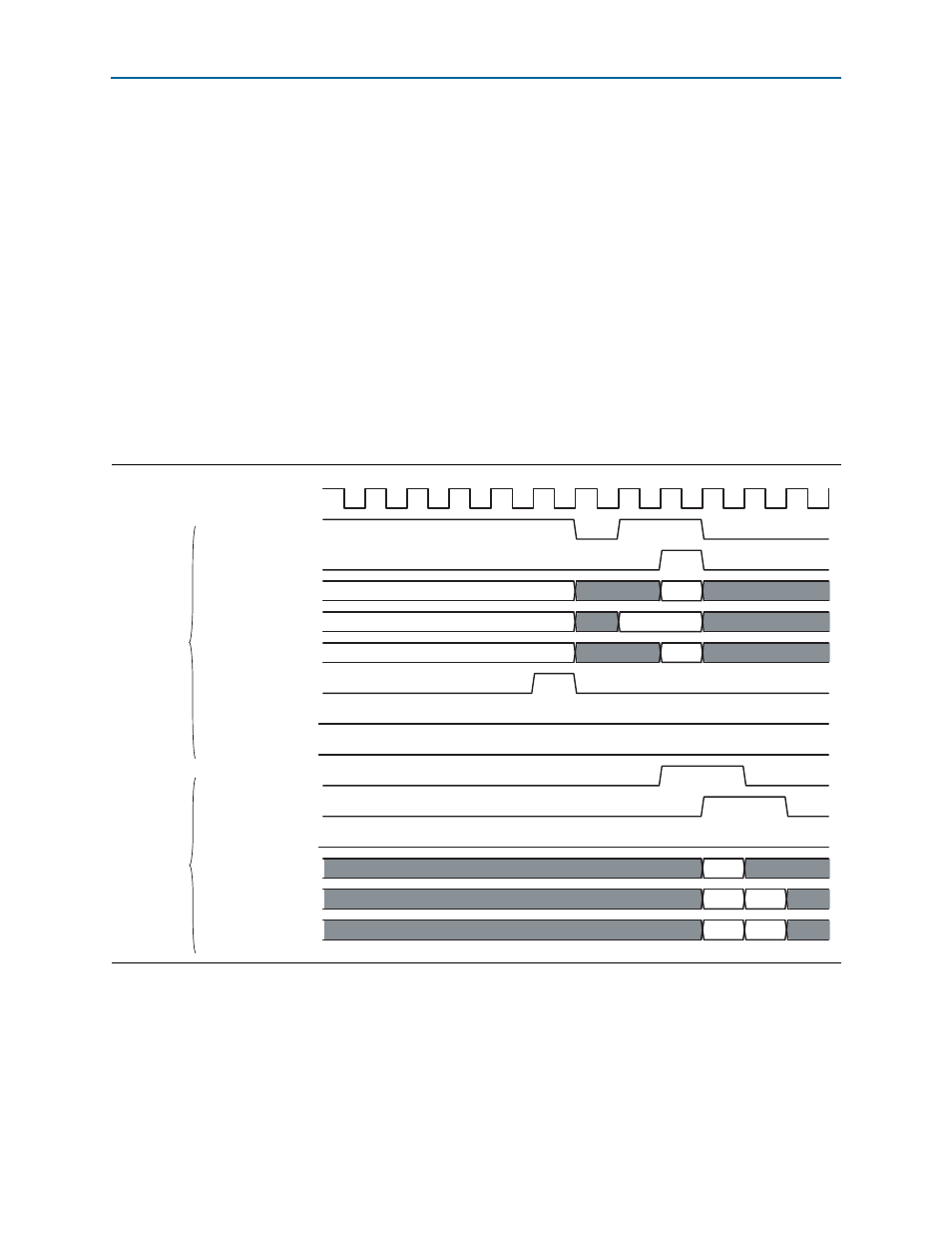

Transaction Aborted

In

, a memory read of 16 DWORDS is sent to the application layer. Having

determined it will never be able to accept the transaction layer packet, the application

layer discards it by asserting rx_abort. An alternative design might implement logic

whereby all transaction layer packets are accepted and, after verification, potentially

rejected by the application layer. An advantage of asserting rx_abort is that

transaction layer packets with data payloads can be discarded in one clock cycle.

Having aborted the first transaction layer packet, the IP core can transmit the second,

a three DWORD completion in this case. The IP core does not treat the aborted

transaction layer packet as an error and updates flow control credits as if the

transaction were acknowledged. In this case, the application layer is responsible for

generating and transmitting a completion with completer abort status and to signal a

completer abort event to the IP core configuration space through assertion of cpl_err.

In clock cycle 6, rx_abort is asserted and transmission of the next transaction begins

on clock cycle number.

Transaction with Data Payload

In

, the IP core receives a completion transaction of eight DWORDS and a

second memory write request of three DWORDS. Bit 2 of rx_data[63:0] is set to 0 for

the completion transaction and to 1 for the memory write request transaction.

Figure B–7. RX Aborted Transaction Waveform

clk

rx_req

rx_ack

rx_desc[135:128]

rx_desc[127:64]

rx_desc[63:0]

rx_abort

rx_retry

rx_mask

rx_dfr

rx_dv

rx_ws

rx_data[63:32]

rx_data[31:0]

rx_be[7:0]

valid

valid

MEMRD 16 DW

CPL 3 DW

valid

valid

DW 1

DW 0

DW 2

0xFF

0x0F

1

2

3

4

5

6

7

8

9

10

11

12

Descriptor

Signals

Data

Signals