For details – Altera IP Compiler for PCI Express User Manual

Page 354

B–36

Chapter :

Recommended Incremental Compilation Flow

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

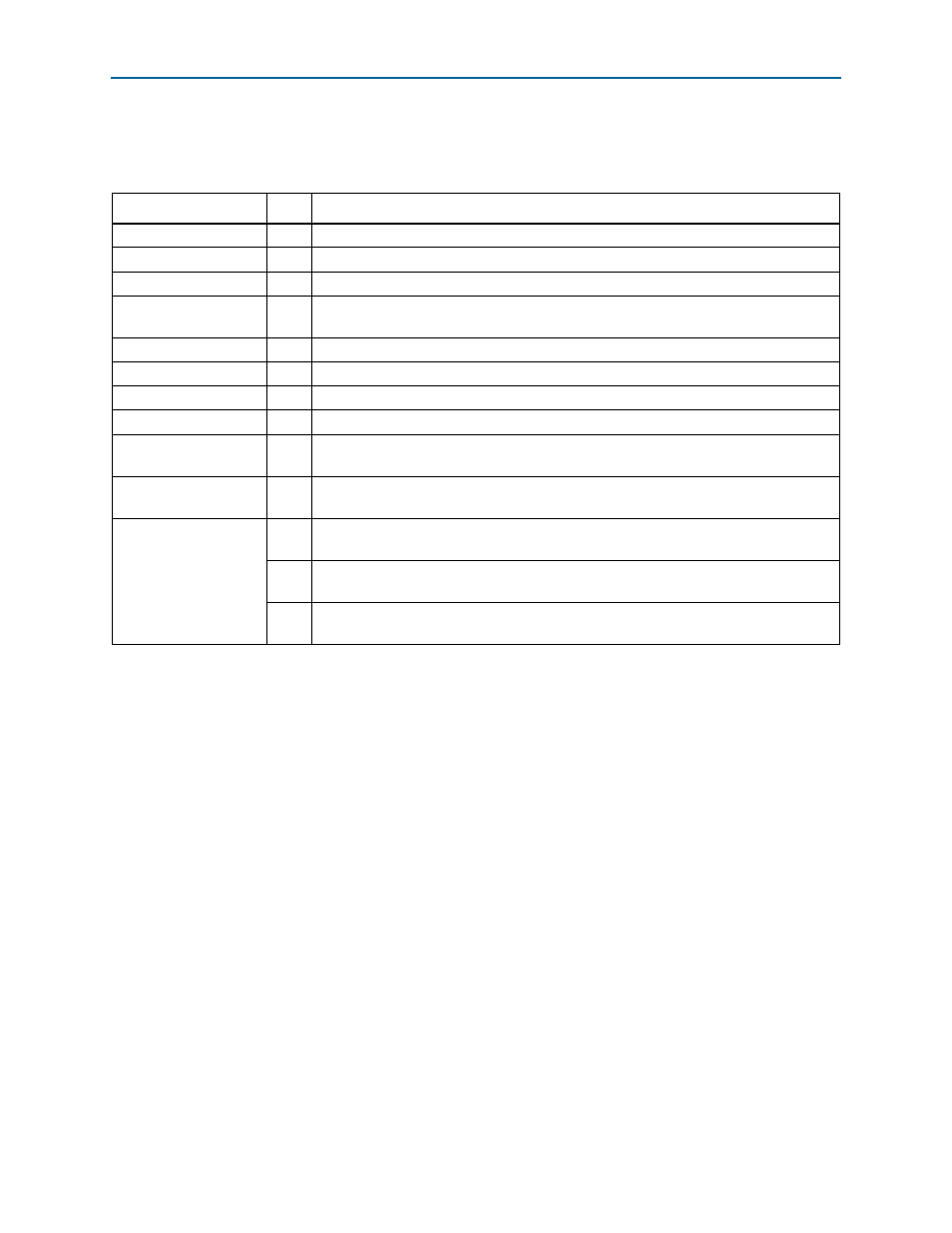

Sideband Interface

describes the application-side sideband signals.

Table B–17. Sideband Signals

Signal

Bit

Description

app_int_sts_icm

—

Same as app_int_sts on the IP core interface. ICM delays this signal by one clock.

cfg_busdev_icm

—

Delayed version of cfg_busdev on the IP core interface.

cfg_devcsr_icm

—

Delayed version of cfg_devcsr on the IP core interface.

cfg_linkcsr_icm

—

Delayed version of cfg_linkcsr on IP core interface. ICM delays this signal by one

clock.

cfg_tcvcmap_icm

—

Delayed version of cfg_tcvcmap on IP core interface.

cpl_err_icm

—

Same as cpl_err_icm on IP core interface

. ICM delays this signal by one clock.

pex_msi_num_icm

—

Same as pex_msi_num on IP core interface

. ICM delays this signal by one clock.

cpl_pending_icm

—

Same as cpl_pending on IP core interface

. ICM delays this signal by one clock.

app_int_sts_ack_ic

m

—

Delayed version of app_int_sts_ack on IP core interface. ICM delays this by one

clock. This signal applies to the ×1 and ×4 IP cores only. In ×8, this signal is tied low.

cfg_msicsr_icm

—

Delayed version of cfg_msicsr on the IP core interface. ICM delays this signal by one

clock.

test_out_icm

[8:0]

This is a subset of test_out signals from the IP core. Refer to

Appendix B

for a

description of test_out.

[4:0]

“ltssm_r” debug signal. Delayed version of test_out[4:0] on ×8 IP core interface.

Delayed version of test_out[324:320] on ×4/ ×1 IP core interface.

[8:5]

“lane_act” debug signal. Delayed version of test_out[91:88] on ×8 IP core interface.

Delayed version of test_out[411:408] on ×4/ ×1 IP core interface.

Notes to

:

(1) Refer to

f or more information.

(2) Refer to

for more information.

(3) Refer to

for more information.