Altera IP Compiler for PCI Express User Manual

Page 215

Chapter 13: Reconfiguration and Offset Cancellation

13–5

Dynamic Reconfiguration

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

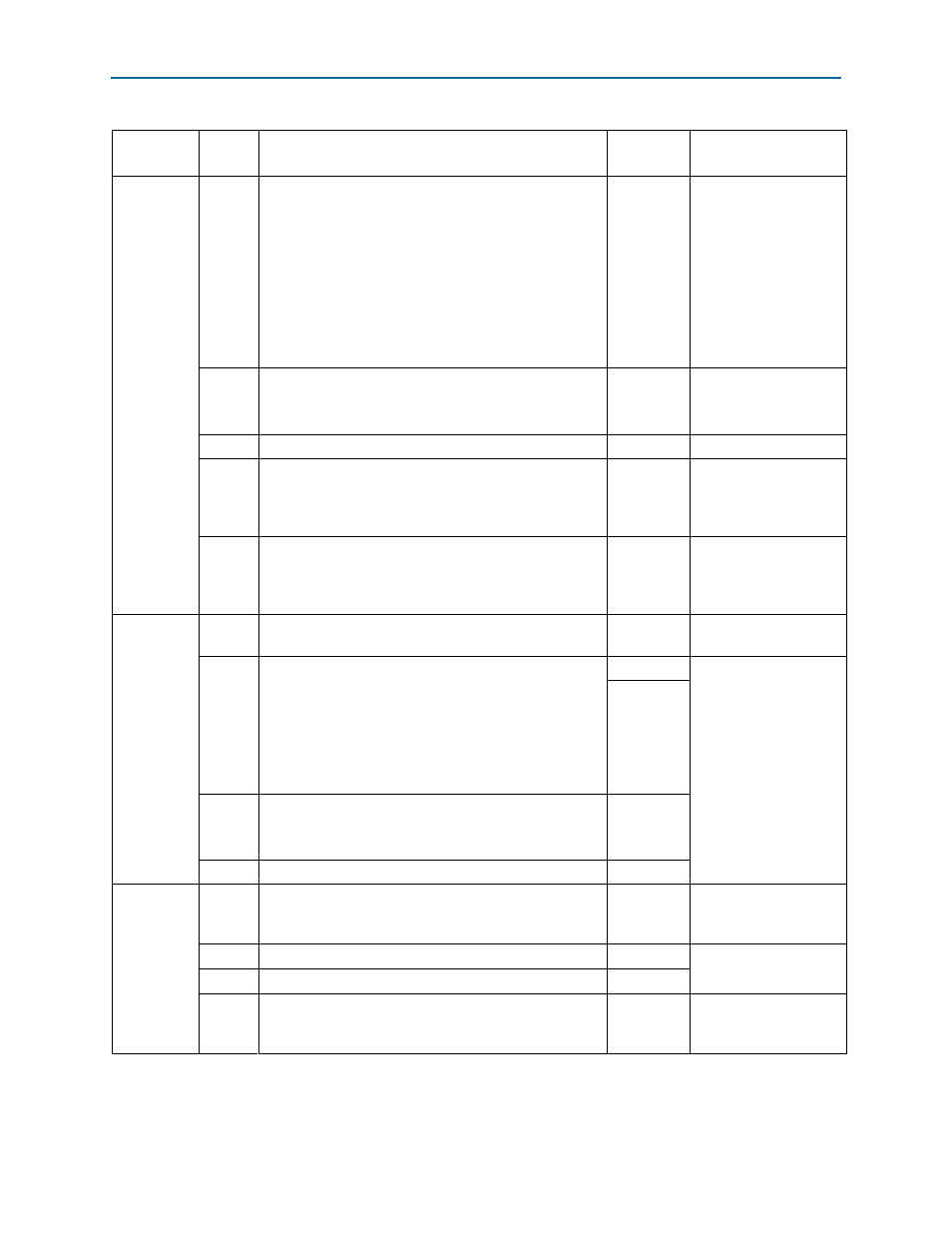

3:0

Completion timeout ranges. The following encodings are

defined:

b’0000

Device Capability

register 2

b’0001: range A.

b’0010: range B.

b’0011: range A&B.

b’0110: range B&C.

b’0111: range A,B&C.

b’1110: range B,C&D.

b’1111: range A,B,C&D.

All other values are reserved.

4

Completion Timeout supported

b’0

Device Capability

register 2

0: completion timeout disable not supported

1: completion timeout disable supported

7:5 Reserved.

b’0

—

8 ECRC generate.

b’0

,

Advanced Error

Capability and Control

register

9 ECRC check.

b’0

,

Advanced Error

Capability and Control

register

10

No command completed support. (available only in PCI

Express Base Specification Revision 1.1 compliant Cores)

b’0

Slot Capability register

13:11

Number of functions MSI capable.

b’010

Message Control

register

b’000: 1 MSI capable.

b’001: 2 MSI capable.

b’010: 4 MSI capable.

b’011: 8 MSI capable.

b’100: 16 MSI capable.

b’101: 32 MSI capable.

14

MSI 32/64-bit addressing mode.

b’1

b’0: 32 bits only.

b’1: 32 or 64 bits

0x96

15 MSI per-bit vector masking (read-only field).

b’0

0 Function supports MSI.

b’1

Message Control

register for MSI

3:1 Interrupt pin.

b’001

—

5:4 Reserved.

b’00

6 Function supports MSI-X.

b’0

Message Control

register for MSI

Table 13–1. Dynamically Reconfigurable Registers in the Hard IP Implementation (Part 4 of 7)

Address

Bits

Description

Default

Value

Additional Information