Icm application-side interface – Altera IP Compiler for PCI Express User Manual

Page 349

Chapter :

B–31

Incremental Compile Module for Descriptor/Data Examples

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

When using the Quartus II software, include the files listed in

in your

design:

ICM Application-Side Interface

Tables and timing diagrams in this section describe the following application-side

interfaces of the ICM:

■

RX ports

■

TX ports

■

MSI port

■

Sideband interface

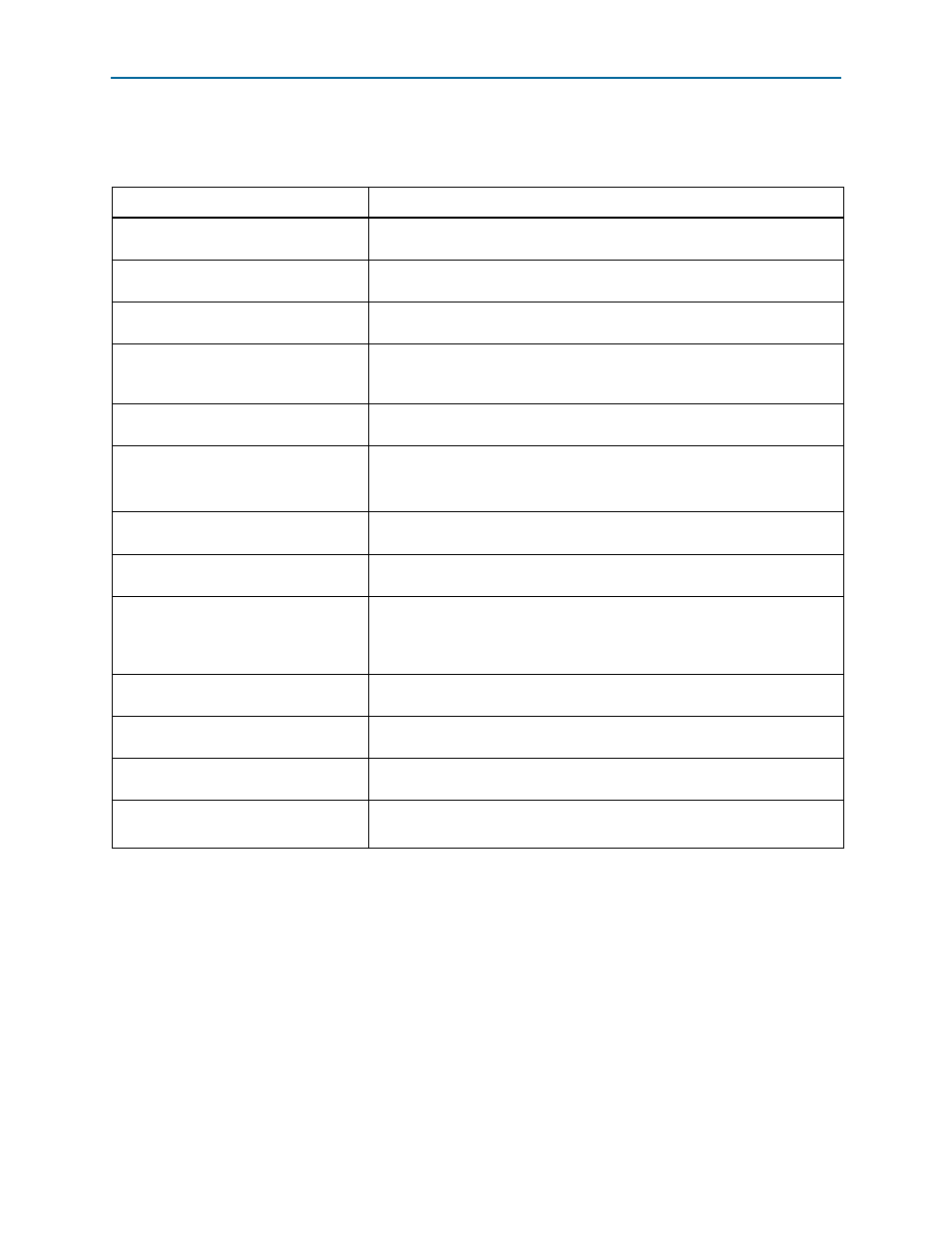

Table B–13. ICM Files

Filename

Description

altpcierd_icm_top.v or

altpcierd_icm_top.vhd

This is the top-level module for the ICM instance. It contains all of the following

modules listed below in column 1.

altpcierd_icm_rx.v or

altpcierd_icm_rx.vhd

This module contains the ICM RX datapath. It instantiates the

altpcierd_icm_rxbridge and an interface FIFO.

altpcierd_icm_rxbridge.v or

altpcierd_icm_rxbridge.vhd

This module implements the bridging required to connect the application’s

interface to the PCI Express transaction layer.

altpcierd_icm_tx.v or

altpcierd_icm_tx.vhd

This module contains the ICM TX and MSI datapaths. It instantiates the

altpcierd_icm_msibridge, altpcierd_icm_txbridge_withbypass, and interface

FIFOs.

altpcierd_icm_msibridge.v or

altpcierd_icm_msibridge.vhd

This module implements the bridging required to connect the application’s

Avalon-ST MSI interface to the PCI Express transaction layer.

altpcierd_icm_txbridge_withbypass.v or

altpcierd_icm_txbridge_withbypass.vhd

This module instantiates the altpcierd_icm_txbridge and

altpcierd_icm_tx_pktordering modules.

altpcierd_icm_txbridge.v or

altpcierd_icm_txbridge.vhd

This module implements the bridging required to connect the application’s

Avalon-ST TX interface to the IP core’s TX interface.

altpcierd_icm_tx_pktordering.v or

altpcierd_icm_tx_pktordering.vhd

This module contains the NP-Bypass function. It instantiates the npbypass FIFO

and altpcierd_icm_npbypassctl.

altpcierd_icm_npbypassctl.v or

altpcierd_icm_npbypassctl.vhd

This module controls whether a Non-Posted PCI Express request is forwarded

to the IP core or held in a bypass FIFO until the IP core has enough credits to

accept it. Arbitration is based on the available non-posted header and data

credits indicated by the IP core.

altpcierd_icm_sideband.v or

altpcierd_icm_sideband.vhd

This module implements incremental-compile boundary registers for the

non-timing critical sideband signals to and from the IP core.

altpcierd_icm_fifo.v or

altpcierd_icm_fifo.vhd

This is a generated RAM-based FIFO.

altpcierd_icm_fifo_lkahd.v or

altpcierd_icm_fifo_lkahd.vhd

This is a generated RAM-based look-ahead FIFO.

altpcierd_icm_defines.v or

altpcierd_icm_defines.vhd

This file contains global define’s used by the Verilog ICM modules.