Altera IP Compiler for PCI Express User Manual

Page 48

3–12

Chapter 3: Parameter Settings

IP Core Parameters

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

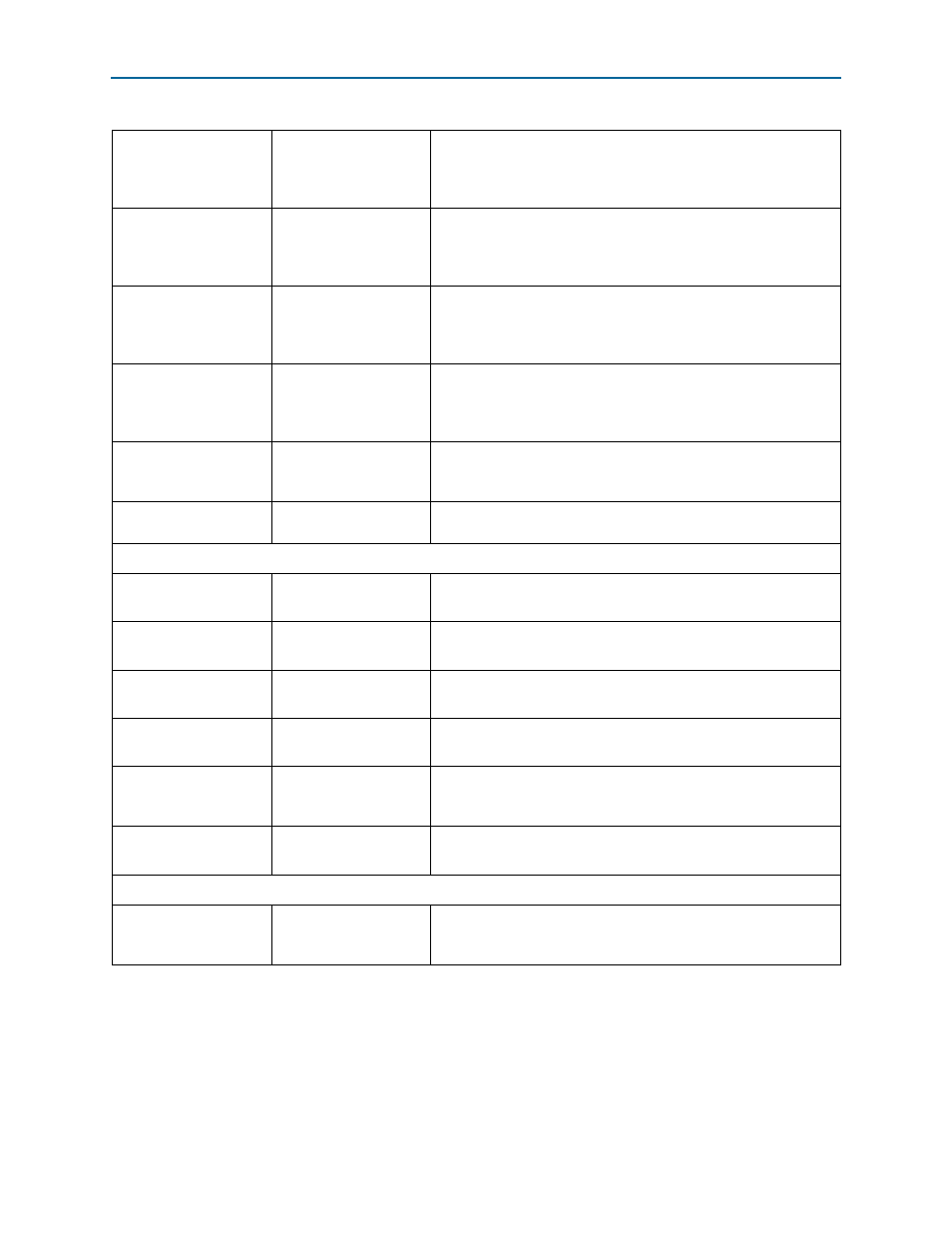

BAR Table (BAR1)

BAR type and size

BAR1 size and type mapping (I/O space

, memory space. BAR0

and BAR1 can be combined to form a 64-bit prefetchable BAR. BAR0

and BAR1 can be configured separate as 32-bit non-prefetchable

memories.)

BAR Table (BAR2)

BAR type and size

BAR2 size and type mapping (I/O space

, memory space. BAR2

and BAR3 can be combined to form a 64-bit prefetchable BAR. BAR2

and BAR3 can be configured separate as 32-bit non-prefetchable

memories.)

BAR Table (BAR3)

BAR type and size

BAR3 size and type mapping (I/O space

, memory space. BAR2

and BAR3 can be combined to form a 64-bit prefetchable BAR. BAR2

and BAR3 can be configured separate as 32-bit non-prefetchable

memories.)

BAR Table (BAR4)

BAR type and size

BAR4 size and type mapping (I/O space

, memory space. BAR4

and BAR5 can be combined to form a 64-bit BAR. BAR4 and BAR5

can be configured separate as 32-bit non-prefetchable

memories.)

BAR Table (BAR5)

BAR type and size

BAR5 size and type mapping (I/O space

, memory space. BAR4

and BAR5 can be combined to form a 64-bit BAR. BAR4 and BAR5

can be configured separate as 32-bit non-prefetchable memories.)

BAR Table (EXP-ROM)

Disable/Enable

Expansion ROM BAR size and type mapping (I/O space, memory

space, non-prefetchable).

PCIe Read-Only Registers

Device ID

0x0004

Sets the read-only value of the device ID register.

Subsystem ID

0x0004

Sets the read-only value of the subsystem device ID register.

Revision ID

0x01

Sets the read-only value of the revision ID register.

Vendor ID

0x1172

Sets the read-only value of the vendor ID register. This parameter

can not be set to 0xFFFF per the PCI Express Specification.

Subsystem vendor ID

0x1172

Sets the read-only value of the subsystem vendor ID register. This

parameter can not be set to 0xFFFF per the

2.0

.

Class code

0xFF0000

Sets the read-only value of the class code register.

Base and Limit Registers

Input/Output

Disable

16-bit I/O addressing

32-bit I/O addressing

Specifies what address widths are supported for the IO base and

IO limit

registers.

Table 3–10. PCI Registers (Part 2 of 3)