Changing from pipe mode to serial mode – Altera IP Compiler for PCI Express User Manual

Page 302

16–14

Chapter 16: Qsys Design Example

Simulating the Qsys System

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

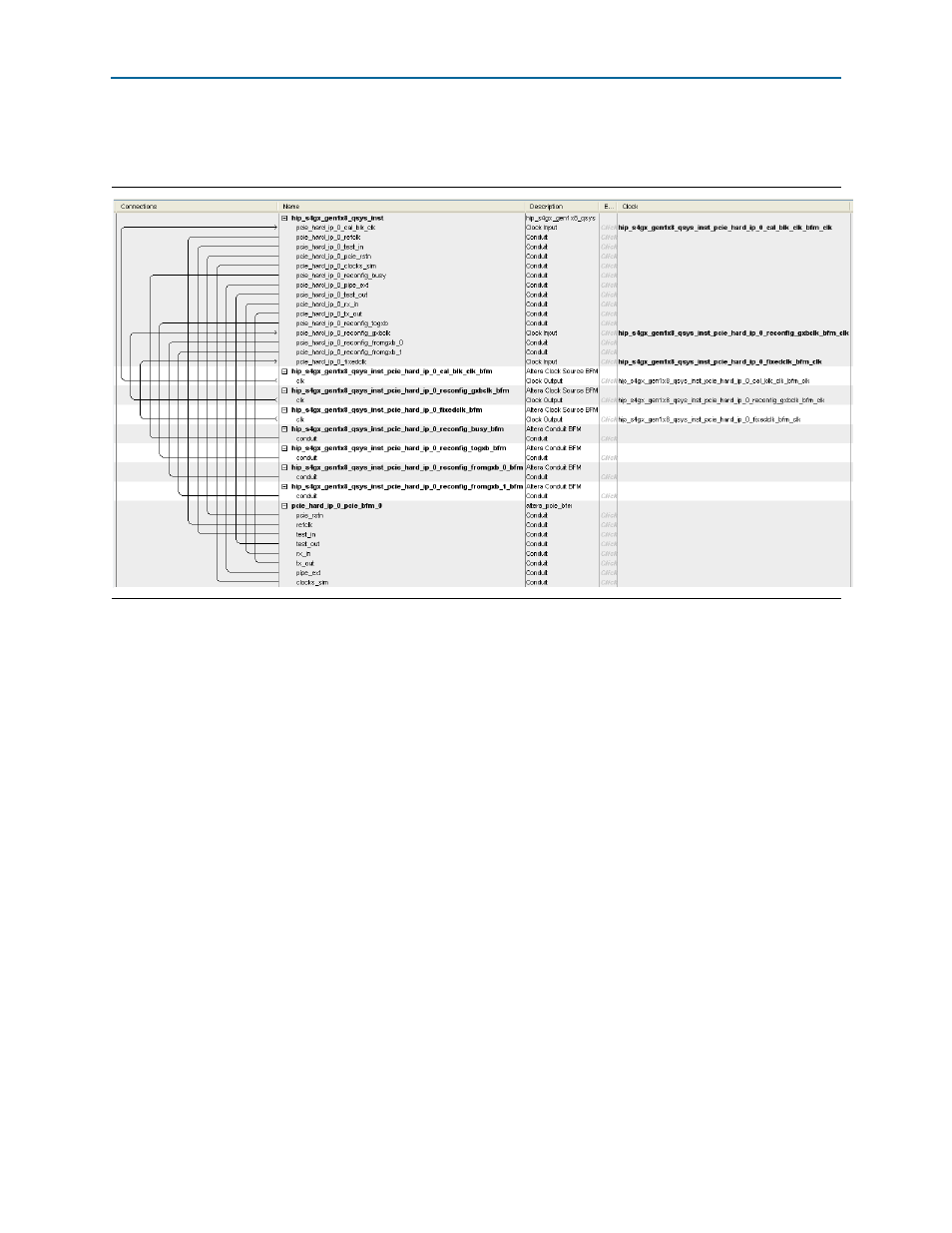

shows the testbench that Qsys creates in

<

project_dir

>/

hip_s4gx_gen1x8_qsys/testbench/hip_s4gx_gen1x8_qsys_tb.qsys

.

The <Quartus II installation

directory>/ip/altera/altera_pcie/altera_pcie_avmm/example_designs/s4gx_gen1x8

folder includes a pregenerated version of the same .qsys file.

Changing from PIPE Mode to Serial Mode

By default, simulation runs in PIPE mode. To run simulation in serial mode, follow

these steps before you begin running the Qsys testbench:

1. Change directory to your project directory subdirectory

hip_s4gx_gen1x8_qsys/testbench/hip_s4gx_gen1x8_qsys_tb/simulation

.

2. Open the file hip_s4gx_gen1x8_qsys_tb.v in a text editor.

3. Find the module instantiation that generates the busy_altgxb_reconfig signal.

The signal has a long prefix in the file and is instantiated in the following code:

hip_s4gx_gen1x8_qsys_tb_hip_s4gx_gen1x8_qsys_inst_pcie_hard_ip_0_reconfig_busy_bfm

hip_s4gx_gen1x8_qsys_inst_pcie_hard_ip_0_reconfig_busy_bfm (

.sig_busy_altgxb_reconfig

(hip_s4gx_gen1x8_qsys_inst_pcie_hard_ip_0_reconfig_busy_bfm_conduit_busy_altgxb_reconfig)

);

4. Replace this module instantiation with the following assignment:

assign hip_s4gx_gen1x8_qsys_inst_pcie_hard_ip_0_reconfig_busy_bfm_conduit_busy_altgxb_reconfig \

= 0;

5. Save and close the file.

6. Change directory to submodules.

Figure 16–5. Qsys Testbench for the IP Compiler for PCI Express Design Example