Altera IP Compiler for PCI Express User Manual

Page 45

Chapter 3: Parameter Settings

3–9

IP Core Parameters

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

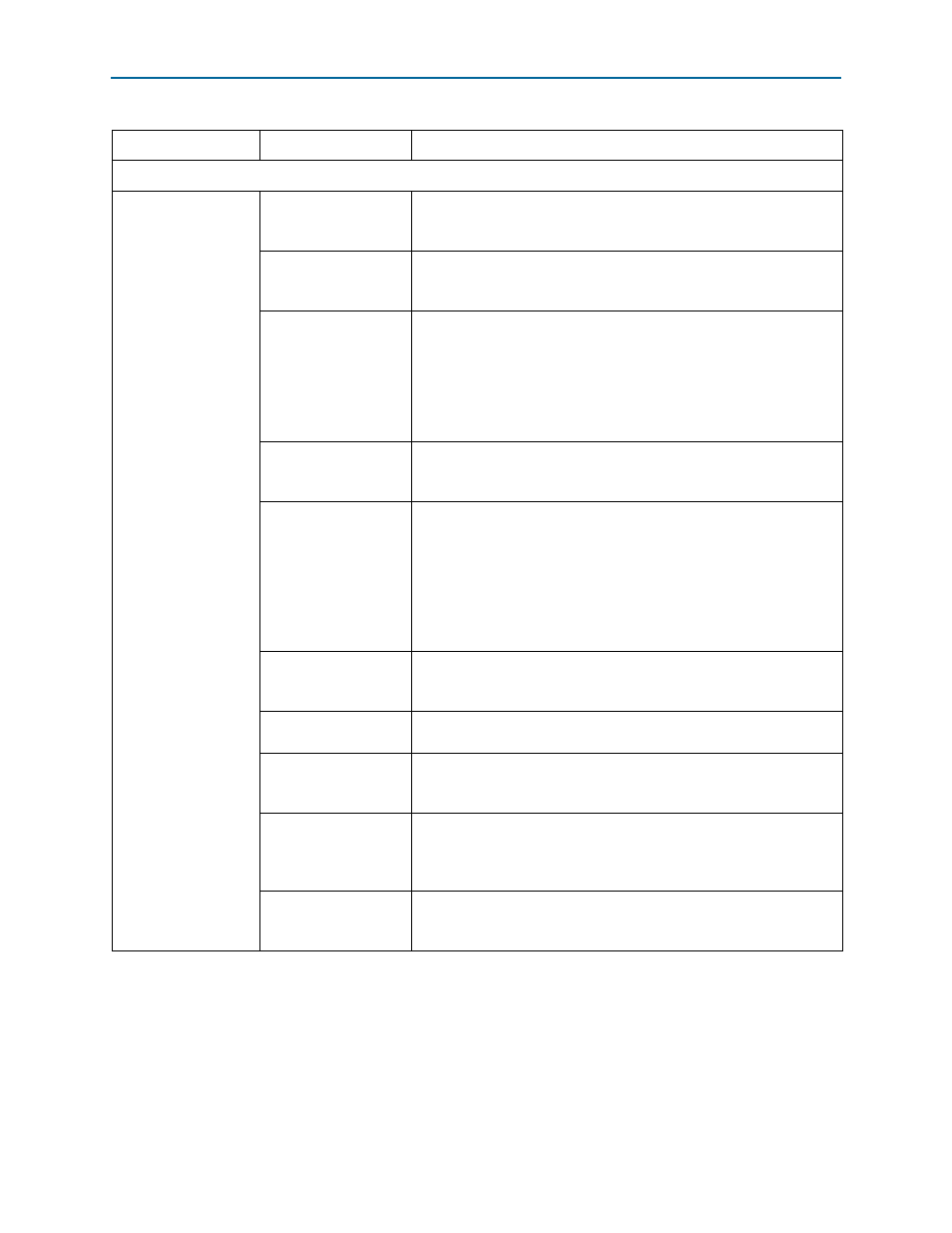

PCIe System Parameters

Custom

Allows all types of external PHY interfaces (except serial). The number of

lanes can be ×1 or ×4. This option is only available for the soft IP

implementation.

Stratix II GX

Serial interface where Stratix II GX uses the Stratix II GX device family's

built-in transceiver. Selecting this PHY allows only a serial PHY interface

with the lane configuration set to Gen1 ×1, ×4, or ×8.

Stratix IV GX

Serial interface where Stratix IV GX uses the Stratix IV GX device

family's built-in transceiver to support PCI Express Gen1 and Gen2 ×1,

×4, and ×8. For designs that may target HardCopy IV GX, the

HardCopy IV GX setting must be used even when initially compiling for

Stratix IV GX devices. This procedure ensures that you only apply

HardCopy IV GX compatible settings in the Stratix IV GX

implementation.

Cyclone IV GX

Serial interface where Cyclone IV GX uses the Cyclone IV GX device

family’s built-in transceiver. Selecting this PHY allows only a serial PHY

interface with the lane configuration set to Gen1 ×1, ×2, or ×4.

HardCopy IV GX

Serial interface where HardCopy IV GX uses the HardCopy IV GX device

family's built-in transceiver to support PCI Express Gen1 and Gen2 ×1,

×4, and ×8. For designs that may target HardCopy IV GX, the

HardCopy IV GX setting must be used even when initially compiling for

Stratix IV GX devices. This procedure ensures HardCopy IV GX

compatible settings in the Stratix IV GX implementation. For Gen2 ×8

variations, this procedure will set the RX Buffer and Retry Buffer to be

only 8 KBytes which is the HardCopy IV GX compatible implementation.

Arria GX

Serial interface where Arria GX uses the Arria GX device family’s built-in

transceiver. Selecting this PHY allows only a serial PHY interface with

the lane configuration set to Gen1 ×1 or ×4.

Arria II GX

Serial interface where Arria II GX uses the Arria II GX device family's

built-in transceiver to support PCI Express Gen1 ×1, ×4, and ×8.

Arria II GZ

Serial interface where Arria II GZ uses the Arria II GZ device family's

built-in transceiver to support PCI Express Gen1 ×1, ×4, and ×8, Gen2

×1, Gen2 ×4.

TI XIO1100

TI XIO1100 uses an 8-bit DDR/SDR with a TXClk or a 16-bit SDR with a

transmit clock PHY interface. Both of these options restrict the number

of lanes to ×1. This option is only available for the soft IP

implementation.

NXP PX1011A

Philips NPX1011A uses an 8-bit SDR with a TXClk and a PHY interface.

This option restricts the number of lanes to ×1. This option is only

available for the soft IP implementation.

Table 3–9. System Settings Parameters (Part 2 of 4)

Parameter

Value

Description