NEC PD78214 User Manual

Page 455

426

µ

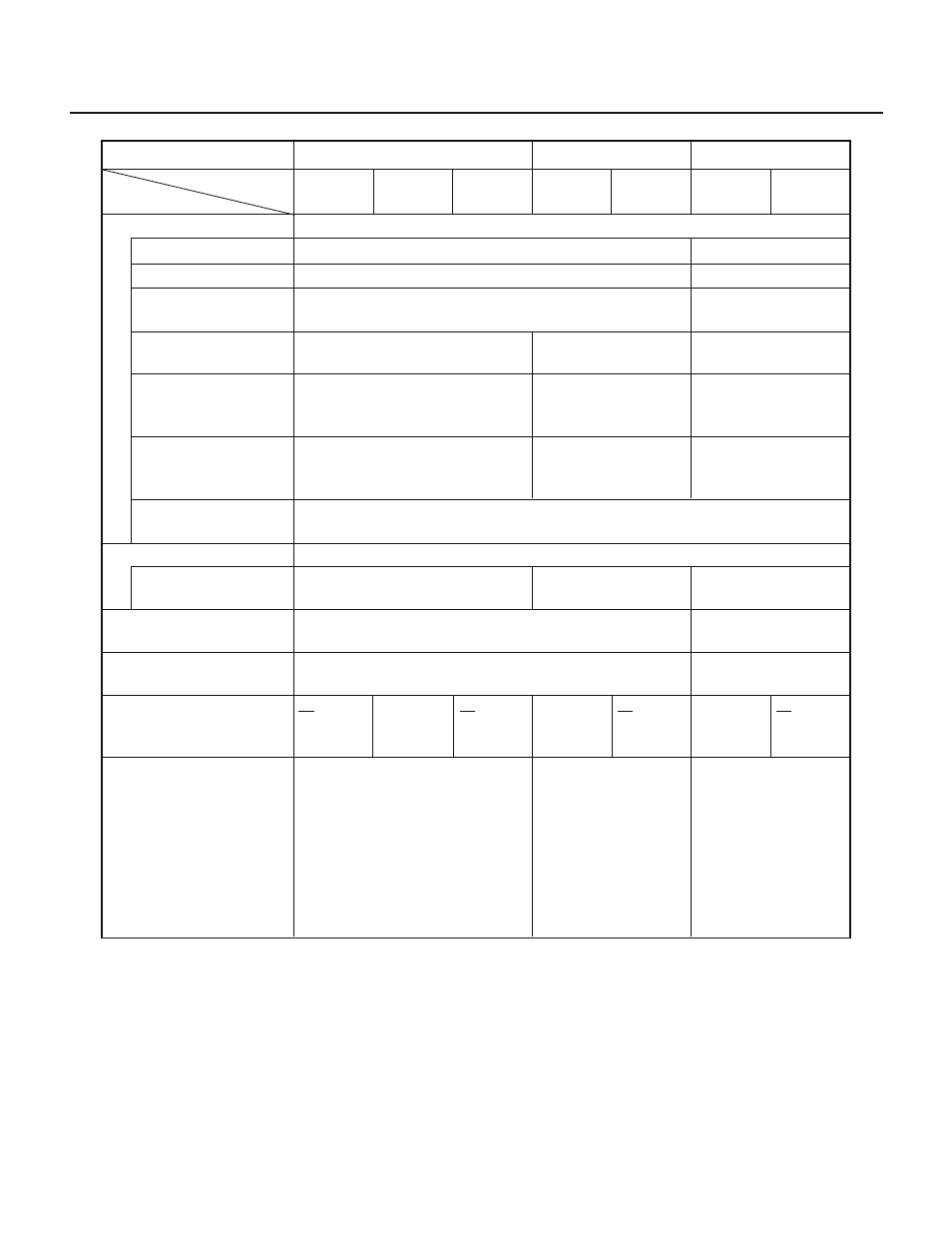

PD78214 Sub-Series

Series name

µPD78214 Sub-Series

µPD78218A Sub-Series

µPD78224 Sub-Series

µPD78214

(

µPD78P214)

Interrupt

µPD78213

µPD78212

µPD78224

(

µPD78P224)

µPD78220

µPD78218A

(

µPD78P218A)

µPD78217A

Product name

Item

7

12

8

9

2 levels (programmable), vector/macro service

8 bits only

8 bits only

External

Internal

Interrupts that can use

macro service

Bits of macro service

counter

Incrementing MPD and

MPT of type C macro

service

Constraints on memory-

to-SFR data transfer by

type A macro service

Macro service execution

time

Standby function

Oscillation setting time

upon releasing STOP mode

Pseudo SRAM refresh

function

Constraints on memory

access

ROM-less mode setting

15

6

8/16 bits selectable

(except type A)

Depends on mode.

Refer to the relevant user's manual.

HALT/STOP mode

Fixed

Fixed

Selected from two

options

Provided (refresh pulse width: 1/f

CLK

)

None

FC80H to FDFFH cannot be

accessed during refresh

Provided (refresh pulse

width: 1.5/f

CLK

)

• 64-pin plastic shrink

DIP (750 mil)

• 64-pin plastic QFP

(14

× 14 mm)

• 64-pin ceramic shrink

DIP with window

(for

µPD78P218A only)

• 64-pin plastic shrink DIP (750 mil)

• 68-pin plastic QFJ (except

µPD78212)

• 64-pin plastic QFP (14

× 14 mm)

• 74-pin plastic QFP (20

× 20 mm)

• 64-pin plastic QUIP (except

µPD78212)

• 64-pin ceramic shrink DIP with

window (for

µPD78P214 only)

• 84-pin plastic QFJ

• 94-pin plastic QFP

(20

× 20 mm)

Package

EA pin =

low level

EA pin =

low level

EA pin =

low level

EA pin =

low level

—

—

—

Increments lower 8 bits

only

(higher bits remain as is)

Occurs when transfer source

buffer (memory) address is

0FED0H to 0FEDFH

Occurs when trans-

ferred data is D0H to

DFH

Increments lower 8 bits only

(higher bits remain as is)

Increments 16 bits

Occurs when transferred data is D0H

to DFH

★