Chapter 7 timer/counter units – NEC PD78214 User Manual

Page 176

147

Chapter 7 Timer/Counter Units

7

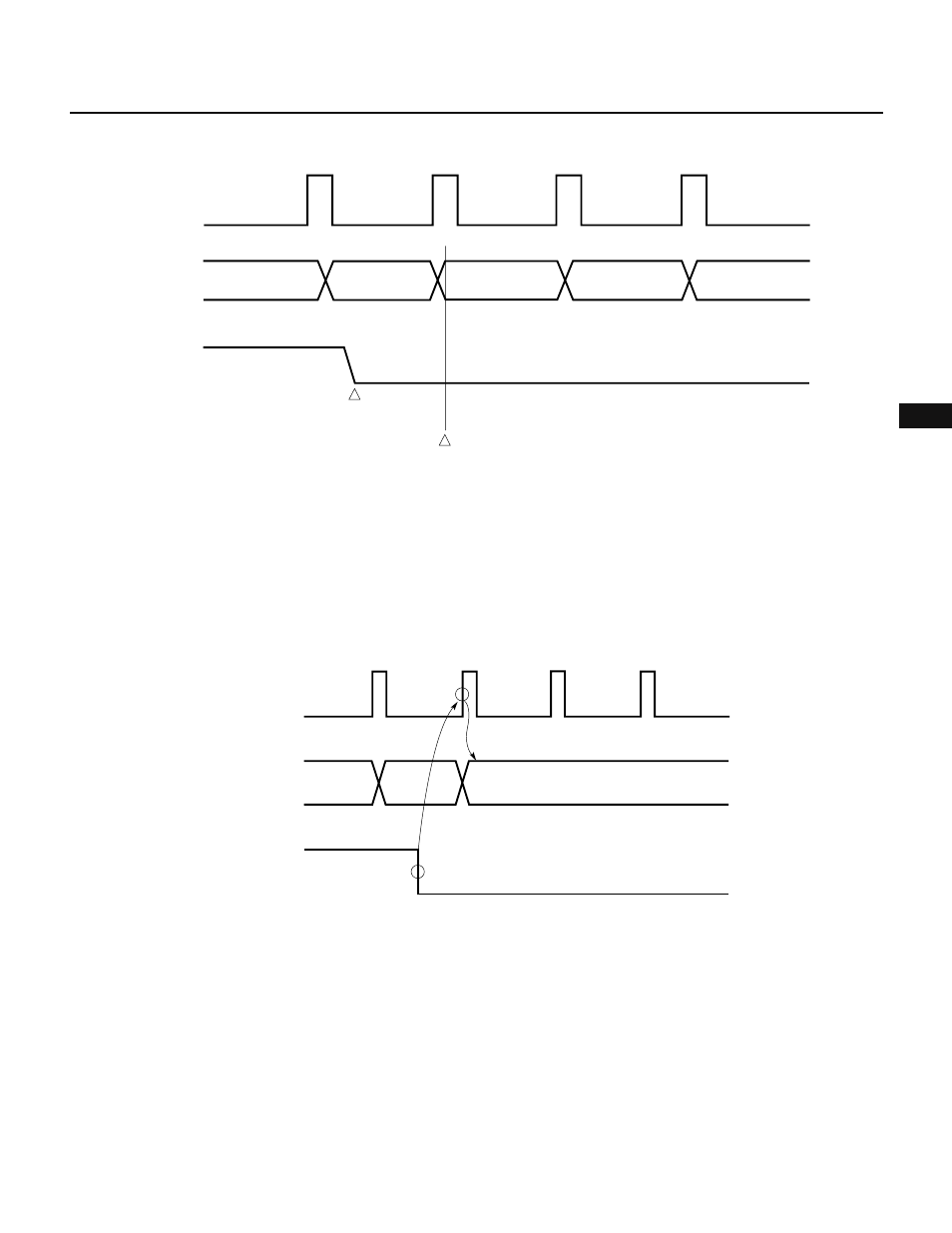

Fig. 7-49 TM1 Cleared after Capture Operation

TM1

Count clock

n-1

n

0

1

2

INTP0

TM1 is captured

to CR11 here

Cleared here

TM1 can also be cleared by software when the CE1 bit of the timer control register (TMC1) is reset to 0.

Similarly, clear operation is performed by the count clock pulse following the resetting of CE1 bit to 0. If the

CE1 bit is set to 1 before TM1 is reset to 0 by the resetting of the CE1 bit to 0 (that is, before the first count clock

pulse is applied after the CE1 bit is reset to 0), two operations are simultaneously performed: one operation

is an operation to clear TM1 to 0, and the other operation is a count operation starting with the counting of

0.

Fig. 7-50 Clear Operation When the CE1 Bit Is Reset to 0

(a) Basic operation

TM1

CE1

n-1

n

0

Count clock