6 notes – NEC PD78214 User Manual

Page 287

258

µ

PD78214 Sub-Series

9.5.3 Example of Setting the BRGC When the External Baud Rate Input (ASCK) Is Used

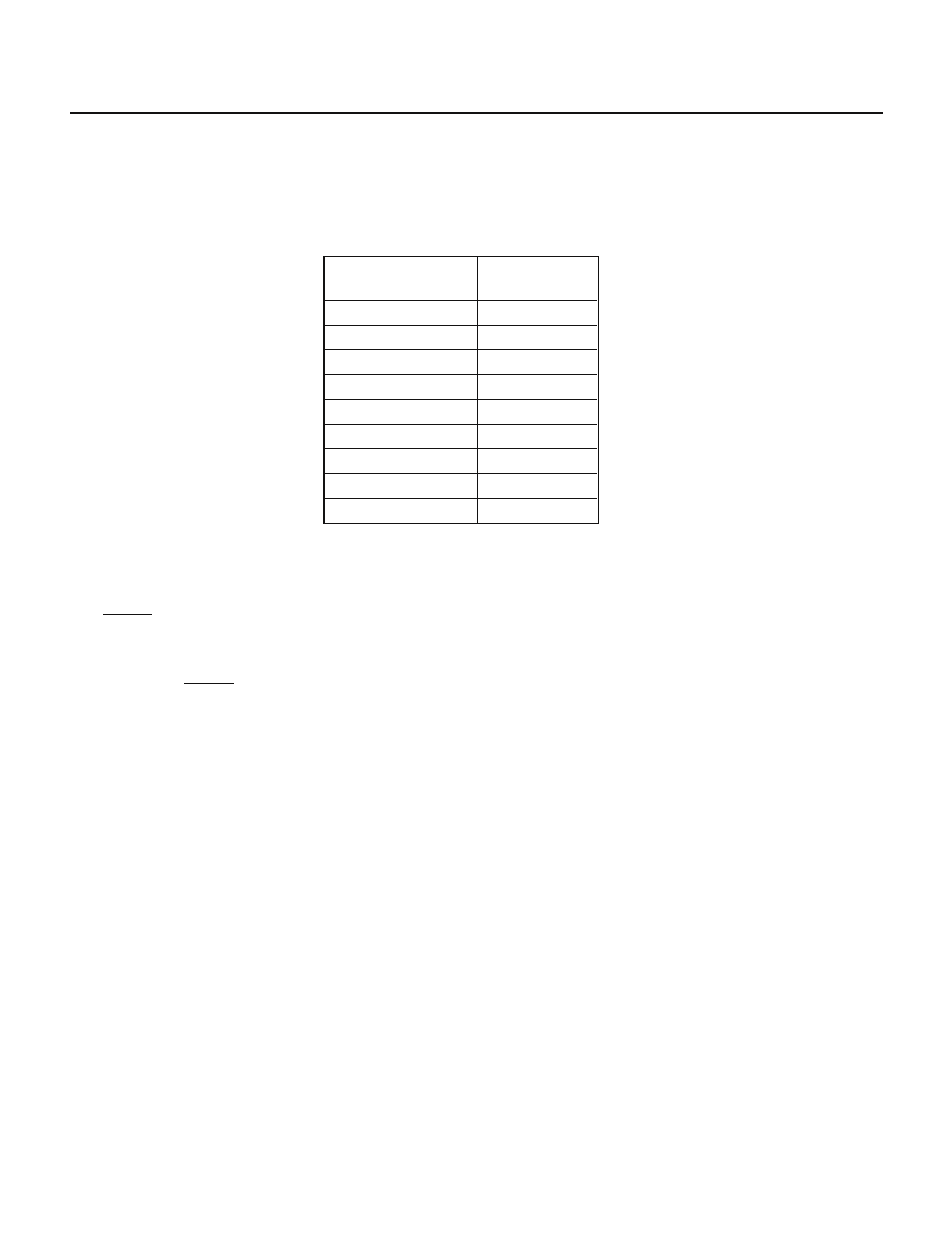

Table 9-5 lists examples of setting the BRGC register when an external baud rate input (ASCK) is used. To use the

ASCK input, set the SCK bit of the asynchronous serial interface mode register (ASIM) to 1.

Table 9-5 Examples of Setting the BRGC When an External Baud Rate Input (ASCK) Is Used

Baud rate [bps]

75

150

300

600

1200

2400

4800

9600

BRGC value

FFH

EFH

DFH

CFH

BFH

AFH

9FH

8FH

f

ASCK

(ASCK input frequency)

153.6 kHz

9.6 NOTES

(1) The asynchronous serial interface mode register (ASIM) must not be modified during transmission. If the

ASIM register is modified during transmission, further transmission becomes impossible (inputting the

RESET signal resumes normal operation).

Software can determine whether transmission is in progress, using the transmission completion interrupt

(INTST) or the interrupt request flag (STIF), which is set by the INTST.

(2) When the RESET signal is input, the transmission shift register becomes empty, but no transmission

completion interrupt occurs. Transmission is triggered by writing the transmit data to the transmission shift

register.

(3) The ASIS register is reset to 0 when the reception buffer (RXB) is read-accessed or receives the next data. To

identify the error, be sure to check the ASIS before reading data from the RXB. If a macro service is used during

reception, it is impossible to identify the error; it is only possible to detect that an error has occurred (an

INTSER has occurs or the reception error interrupt request flag (SERIF) is set to 1). Make sure that this poses

no problem for your application.

(4) If the ASIM register is modified during reception, the current and next receive data may become undefined.

When changing the mode, disable reception beforehand.

(5) Be sure to read the reception buffer (RXB) contents, even if a reception error occurs. Otherwise, an overrun

error will occur when the next data is received, and the error status will persist.

(6) Do not write to the BRGC register during communication. If a write instruction is executed for the BRGC

register, the 4-bit counter and frequency divider are reset, and the baud rate clock generated is disturbed,

hampering normal communication.