10 ppg output, Chapter 7 timer/counter units – NEC PD78214 User Manual

Page 214

185

Chapter 7 Timer/Counter Units

7

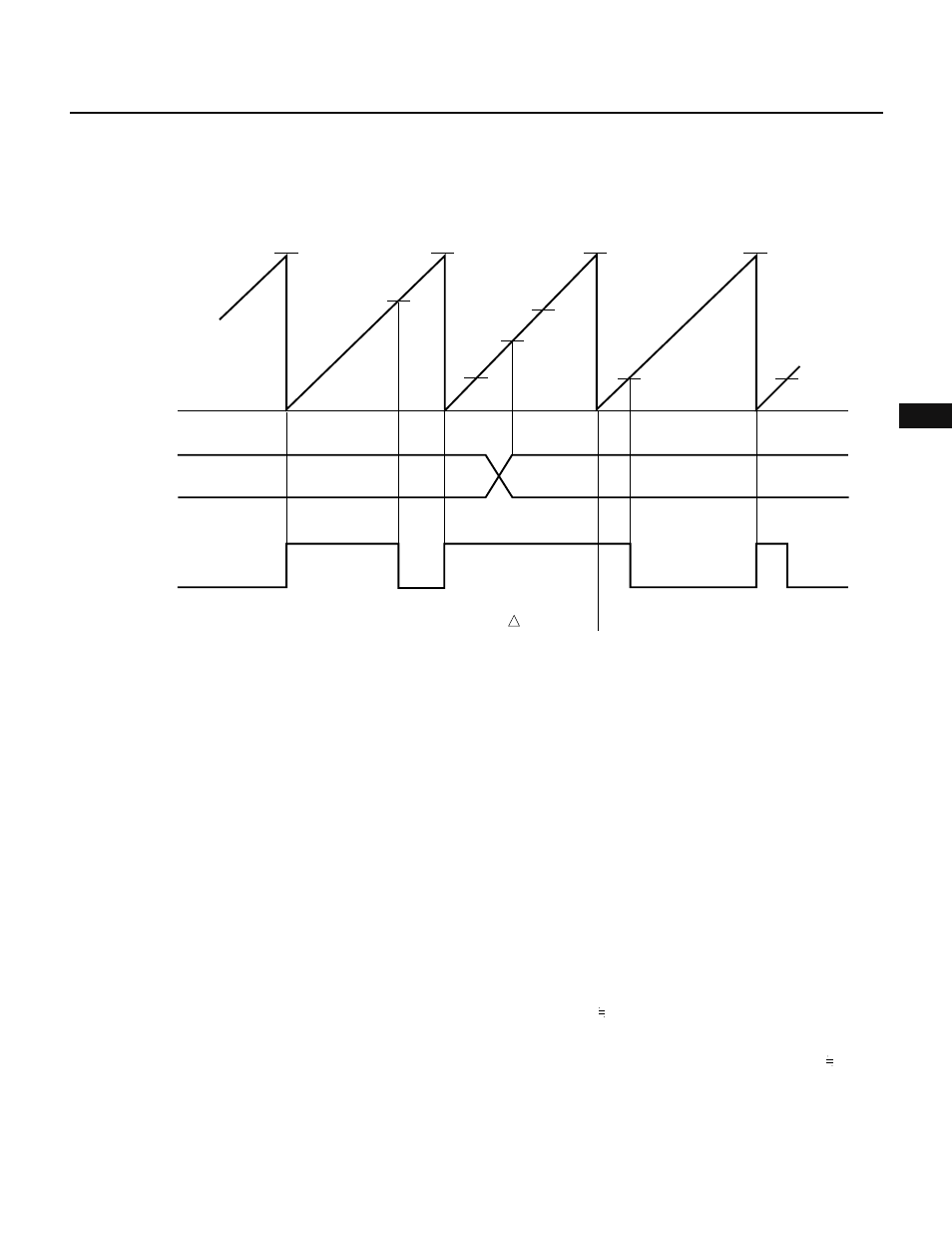

Cautions 1. If a value less than the value of 8-bit timer 2 (TM2) is set in a compare register (CR20, CR21), a PWM signal with a 100% duty

factor is output. Rewrite the CR20 or CR21 compare register, if required, by using an interrupt generated by a coincidence

between TM2 and the compare register.

Fig. 7-89 Example of PWM Output Signal with a 100% Duty Factor

TO2

CR20

0H

n1

n2

n2

n2

n2

n3

n1

FFH

TM2

count value

When a value, n2 less than TM2 value, n3 is written to CR20

here, the duty factor is 100% during this period.

n1

FFH

FFH

FFH

Remark ALV2 = 0

2. If timer output is disabled (ENTOn = 0: n = 2, 3), the output level on the TOn (n = 2, 3) is the inverted value of the value set in

ALVn (n = 2, 3). Accordingly, note that if timer output is disabled when the PWM output function is selected, the active level

is output.

7.3.10 PPG Output

The PPG output function outputs a square wave that has a period determined by the CR21 compare register, and

has a pulse width determined by the CR20 compare register. PPG output is PWM output whose period is made

variable. This output signal can be output on the TO0 pin only.

Before this function can be used, the CLR21 bit of capture/compare control register 2 (CRC2) must be set to 1, the

CLR22 bit of the same register must be set to 0, and the CMD2 bit of timer control register 1 (TMC1) must be set

to 0.

The pulse period and pulse width are as follows:

• PPG period = ((value set in CR21 compare register) + 1)

× x/f

CLK

; x = 16, 32, 64, 128, 256, 512

• PPG pulse width = ((value set in CR20 compare register)

× x + 2)/f

CLK

(value set in CR20)

× x/f

CLK

where, CR20

≤ CR21

• Duty factor = (PPG pulse width)/(PPG period) = ((value set in CR20)

× x + 2)/(((value set in CR21) + 1) × x) (value

set in CR20)/((value set in CR21) + 1)

Caution In PPG output, the actual pulse width is longer than a value obtained with the approximate expression by two clock pulses of

f

CLK

for the active level, and is shorter than such an approximate value by two clock pulses of f

CLK

for the inactive level. Take

this point into consideration when high-precision output is required, the PPG pulse period is short, or a high-speed count clock

is used.