1 interrupt request sources, 1 software interrupt request – NEC PD78214 User Manual

Page 331

302

µ

PD78214 Sub-Series

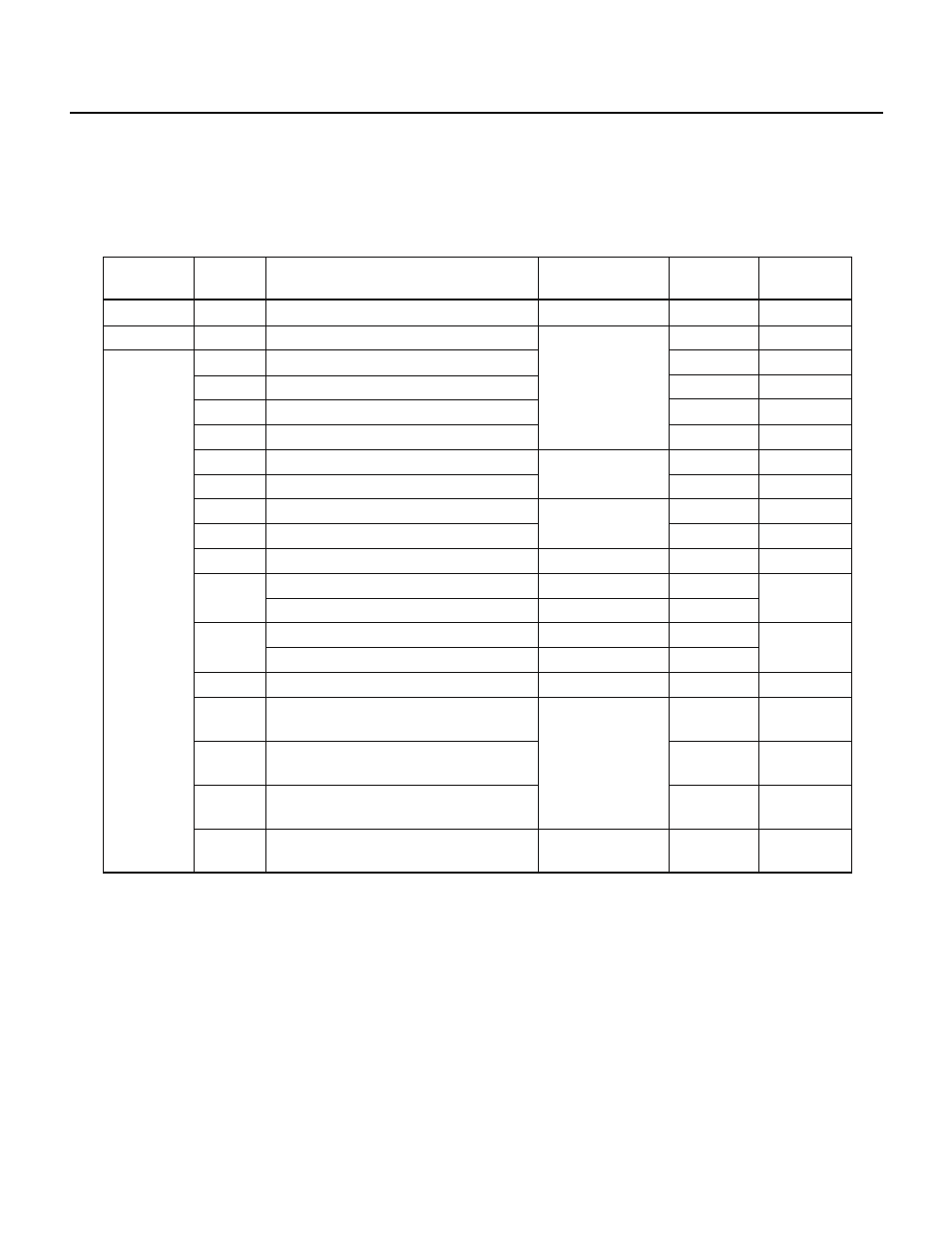

12.1 INTERRUPT REQUEST SOURCES

The

µPD78214 has 19 interrupt request sources shown in Table 12-2. Each of these sources is assigned an interrupt

vector table.

Table 12-2 Interrupt Request Sources

Software

Nonmaskable

Maskable

Interrupt

request type

None

None

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

BRK instruction execution

NMI (edge input to the pin is detected)

INTP0 (edge input to the pin is detected)

INTP1 (edge input to the pin is detected)

INTP2 (edge input to the pin is detected)

INTP3 (edge input to the pin is detected)

INTC00 (TM0-CR00 coincidence signal generation)

INTC01 (TM0-CR01 coincidence signal generation)

INTC10 (TM1-CR10 coincidence signal generation)

INTC11 (TM1-CR11 coincidence signal generation)

INTC21 (TM2-CR21 coincidence signal generation)

INTP4 (edge input to the pin is detected)

INTC30 (TM3-CR30 coincidence signal generation)

INTP5 (edge input to the pin is detected)

INTAD (A/D conversion end)

INTC20 (TM2-CR20 coincidence signal generation)

INTSER (asynchronous serial interface recep-

tion error occurrence)

INTSR (asynchronous serial interface reception

end)

INTST (asynchronous serial interface transmis-

sion end)

INTCSI (clock-synchronized serial interface

transmission end)

Macro

service type

None

None

A, B

A, B

A, B

B

B

B

A, B, C

A, B, C

A, B

B

A, B

B

A, B

A, B

None

A, B

A, B

A, B

Vector table

address

003EH

0002H

0006H

0008H

000AH

000CH

0014H

0016H

0018H

001AH

001CH

0012H

0020H

0022H

0024H

0026H

000EH

0010H

Interrupt request source

Generating unit

Default

priority

Edge detection

16-bit timer/counter

8-bit timer/counter 1

8-bit timer/counter 2

Edge detection

8-bit timer/counter 3

Edge detection

A/D converter

8-bit timer/counter 2

Asynchronous serial

interface

Clock-synchronized

serial interface

Remark The default priority is fixed by hardware. If two or more interrupts having the same priority occur simultaneously, they are handled

according to their default priority.

12.1.1 Software Interrupt Request

A software interrupt request is issued by the BRK instruction, which eventually causes a vectored interrupt.

Interrupt requests issued by the BRK instruction are accepted even in an interrupt disabled state. In this case,

interrupt priority control is not applied.

When the BRK instruction is executed, the vector table contents are unconditionally set in the PC to cause a branch.

By executing the BRK instruction in a BRK service routine, the service routine can nest itself.

To exit the BRK service routine, execute the RETB instruction.