4 stop mode, 2 releasing stop mode – NEC PD78214 User Manual

Page 411

382

µ

PD78214 Sub-Series

14.4 STOP MODE

14.4.1 Specifying STOP Mode and Operation States in STOP Mode

The system enters STOP mode when the STP bit of the STBC register is set to 1.

The STBC register can be written only with a specified 8-bit data write instruction. To specify STOP mode, execute

the “MOV STBC, #02H” instruction.

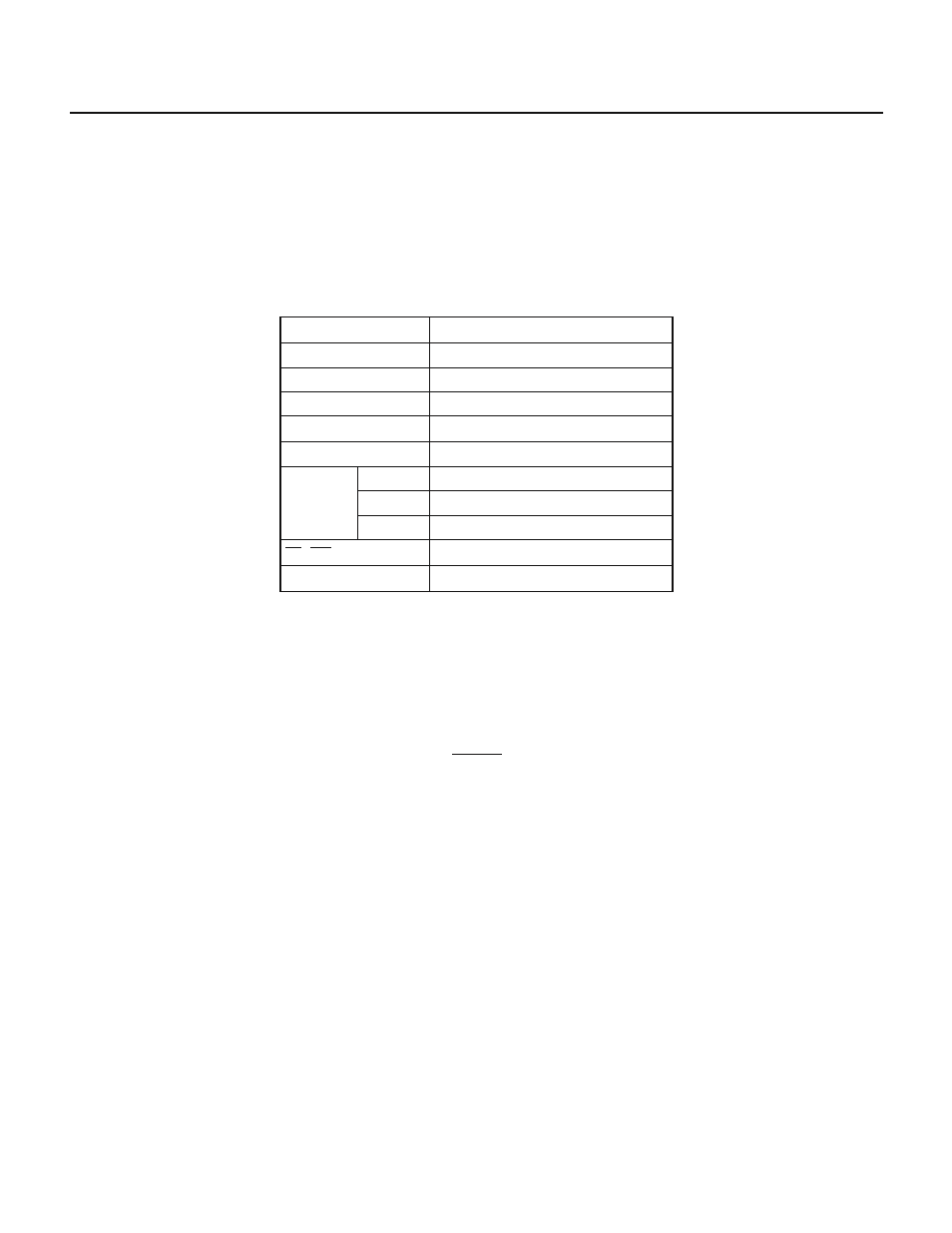

Table 14-4 Operation States in STOP Mode

Clock oscillator

Internal system clock

CPU

I/O lines

Peripheral functions

Internal RAM

AD0-AD7

Bus lines

A8-A15

A16-A19

RD, WR output

ASTB output

Operating

Operating

Stopped

Same as before entering STOP mode

Stopped

Note

Contents maintained

High-impedance

States maintained

Low

High

Low

Note The A/D converter stops, but its current dissipation is not reduced if the CS bit of the A/D converter mode register (ADM) is set.

Cautions 1. In STOP mode, the X1 pin is internally short-circuited to V

SS

(ground potential) to prevent current leakage from the clock

oscillator circuit. STOP mode must not, therefore, be specified for a system using an external clock.

2. Reset the CS bit for the A/D converter.

3. The system enters STOP mode even if an NMI request is being held when STOP mode is specified. When using an NMI request

to release STOP mode, input the NMI signal again.

14.4.2 Releasing STOP Mode

STOP mode can be released by inputting an NMI or RESET signal.

(1) Releasing STOP mode by NMI input

(a) Operation

The oscillator restarts when an effective edge, specified with the external interrupt mode register

(INTM0), is detected at the NMI pin. Then, STOP mode is released after the specified time, required to

allow the oscillation to settle, has elapsed.

Once STOP mode has been released, processing branches to the NMI service program if the NMIS bit of

the interrupt status register (IST) is set to 0. If the NMIS bit is set to 1 (for example, when STOP mode

is specified in the NMI interrupt service program), processing is resumed from the instruction subsequent

to that which specified STOP mode. Processing then branches to the NMI interrupt service program when

the NMIS bit is set to 0 (for example, with a RETI instruction).

(b) Oscillation settling time

The oscillator restarts when an effective, edge specified with the external interrupt mode register

(INTM0), is detected at the NMI pin. Then, when the input level of the NMI signal returns to its original

level, the oscillation settling time counter starts counting. When the 16-bit counter overflows (in 11 ms

when f

XX

= 12 MHz), the internal system clock is started. The system therefore waits, from the detection

of the effective edge to the start of the internal clock, a total time equal to the high- or low-level width of

the NMI signal after detecting the effective edge and the time needed for the 16-bit oscillation settling time

counter to overflow.