3 operation – NEC PD78214 User Manual

Page 397

368

µ

PD78214 Sub-Series

13.5.3 Operation

(1) Pulse refresh operation

To support the pulse refresh cycle of pseudo static RAM, the REFRQ pin outputs refresh pulses, synchronized

with the bus cycle.

Adjust the oscillator frequency and bits 1 and 0 (RFT1 and RFT0) of the refresh mode register (RFM) so that

at least 512 refresh pulses are output in 8 ms.

Table 13-2 System Clock Frequency and Refresh Pulse Output Cycle When Pseudo Static RAM Is Used

64/f

CLK

32/f

CLK

16/f

CLK

System clock frequency

(f

CLK

) MHz

4.096 < f

CLK

≤ 6

(8.192 < f

XX

≤ 12)

2.048 < f

CLK

≤ 4.096

(4.096 < f

XX

≤ 8.192)

2 < f

CLK

≤ 2.048

(4

≤ f

XX

≤ 4.096)

Refresh pulse output cycle

0

1

0

1

0

0

RFT1

RFT0

Pulse refresh is controlled so that it does not overlap external memory access. During the refresh cycle, the

external memory access cycle is held pending (ASTB, RD, and WR are inactive). During the external memory

access cycle, the refresh cycle is held pending.

When pulse refresh does not cause a contention with external memory access, the refresh cycle can be

executed without affecting instruction execution by the CPU.

(a) Accessing internal memory

Even when external pseudo static RAM is not accessed, and internal memory is accessed, the refresh bus

cycle is output at the intervals specified by the RFM register, ensuring that the contents of pseudo static

RAM are retained.

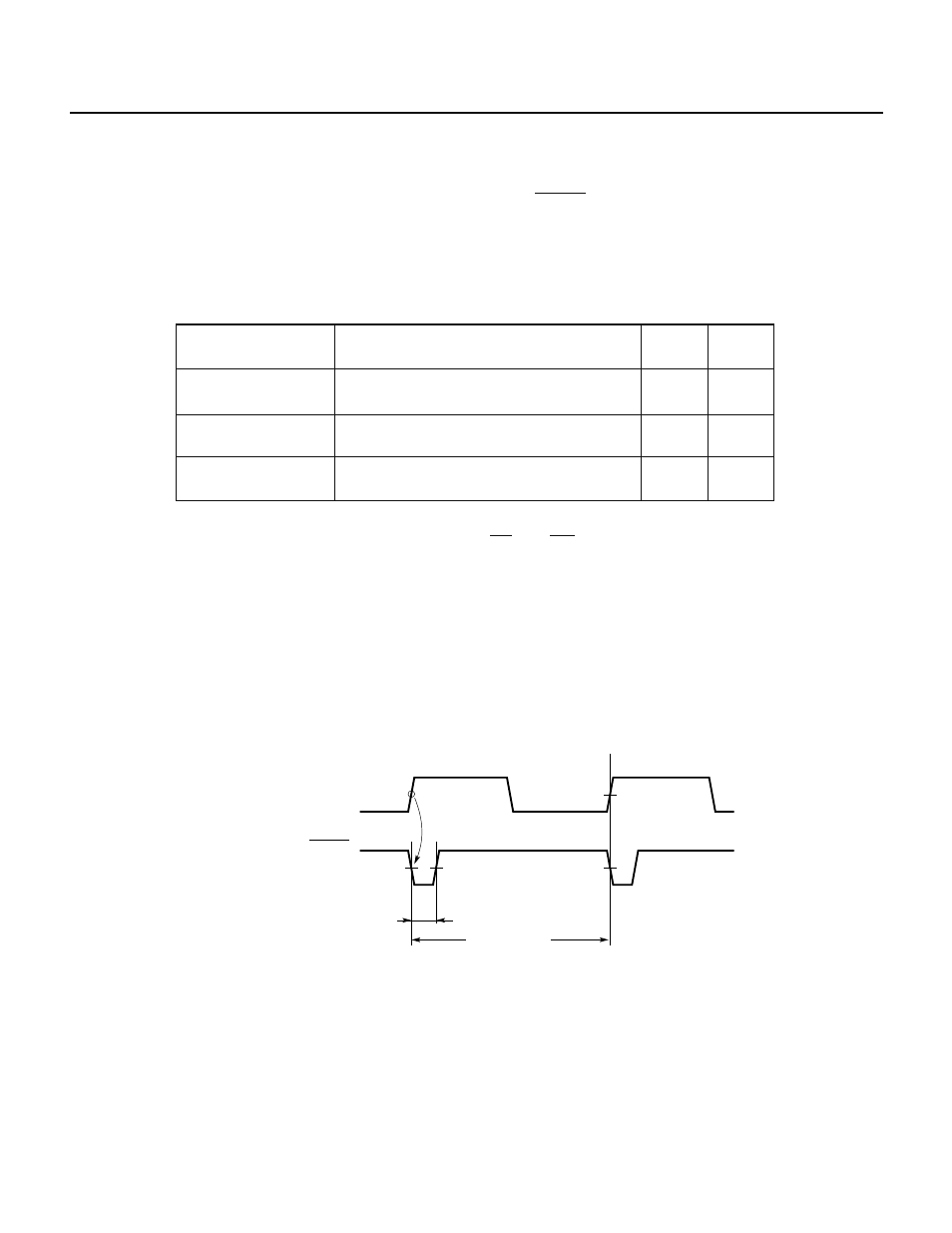

Fig. 13-19 Pulse Refresh When Internal Memory Is Accessed

1t

CYC

Refresh cycle

REFRQ

pin output

t

CYC

: system clock cycle time (1/f

CLK

) [ns] (f

CLK

= 6 MHz)

Refresh timing counter