4 multiple-interrupt handling, Chapter 12 interrupt functions – NEC PD78214 User Manual

Page 342

313

Chapter 12 Interrupt Functions

12

12.3.4 Multiple-Interrupt Handling

The

µPD78214 performs multiple-interrupt handling in which another interrupt request is accepted during one

interrupt is already being handled. Multiple-interrupt handling runs according to priority.

Priority control is based on either default priority or programmable priority specified in the priority specification

flag register (PR0). Priority control by default priority handles interrupt requests according to the default priority

assigned to each interrupt request (see Table 12-2). Priority control by programmable priority divides interrupt

requests into a high-priority group and a low-priority group according to the corresponding bit of the PR0 register.

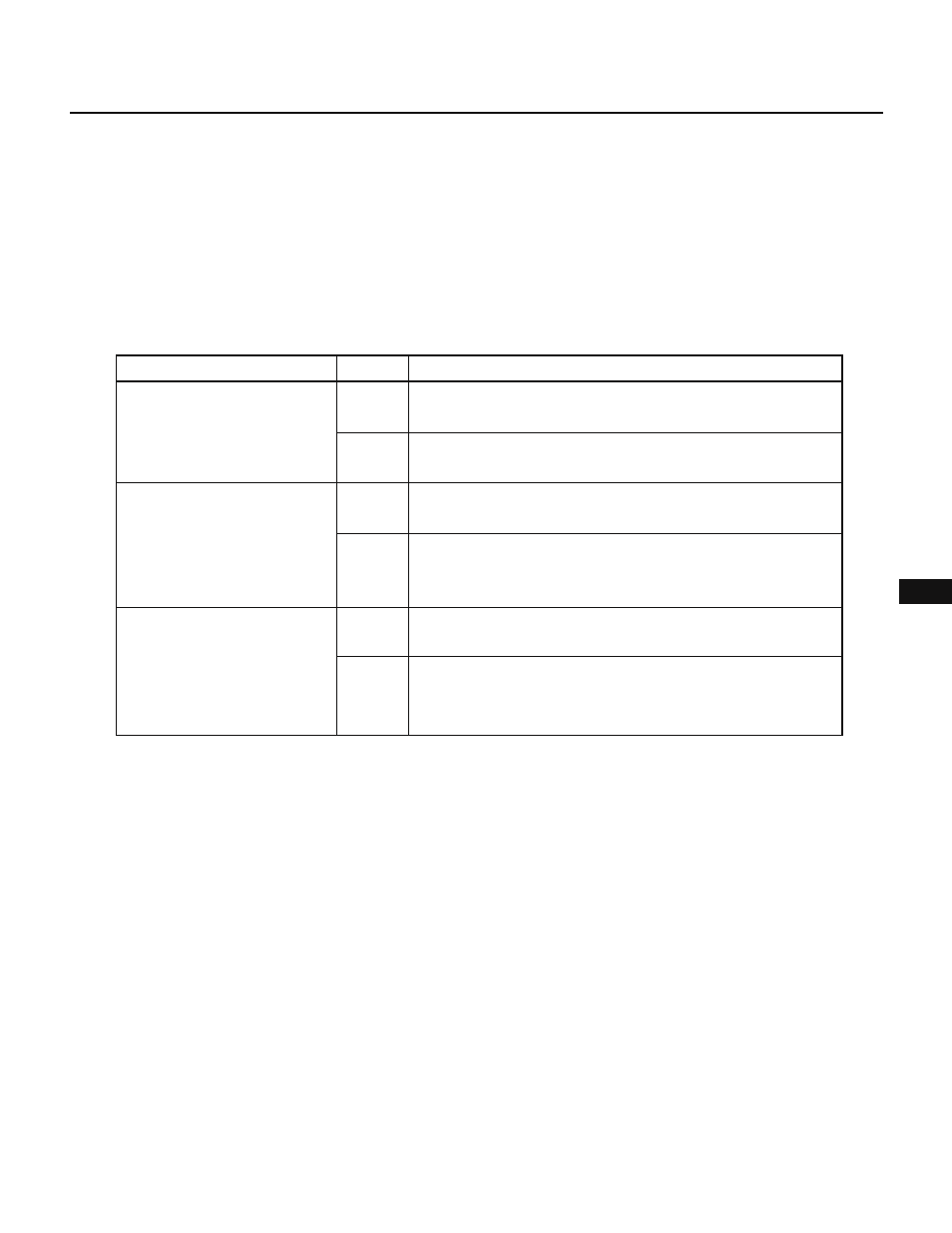

Table 12-4 lists interrupt requests that can be subjected to multiple-interrupt handling.

Table 12-4 Multiple-Interrupt Handling

Interrupts assigned low pro-

grammable priority

Interrupts assigned high

programmable priority

Nonmaskable interrupt

• Nonmaskable interrupt

• Maskable interrupt by macro service processing

• Nonmaskable interrupt

• All maskable interrupts

• Nonmaskable interrupt

• Maskable interrupt by macro service processing

• Nonmaskable interrupt

• Maskable interrupt by macro service processing

• Maskable interrupt assigned high programmable priority

• Nonmaskable interrupt

Note 2

• Maskable interrupt by macro service processing

• Nonmaskable interrupt

Note 2

• Maskable interrupt by macro service processing

• Maskable interrupt assigned high programmable priority

Note 3

Interrupt request accepted

Interrupt request source that can be subjected to multiple-interrupt handling

IE flag

0

1

Note 1

0

0

1

Note 1

1

Note 1

Notes 1. Immediately after an interrupt is accepted, interrupts are disabled (IE = 0) automatically. To enable interrupts (IE = 1), execute the

EI instruction.

2. When a nonmaskable interrupt request is being accepted, bit 0 (NMIS) of the interrupt status register (IST) is 1.

When the NMIS bit is 1, nonmaskable interrupt requests are not accepted. To enable multiple-interrupt handling for nonmaskable

interrupt requests, reset the NMIS flag to 0 by software.

3. When the ISP flag is 1, low priority interrupt requests are accepted.