Chapter 7 timer/counter units – NEC PD78214 User Manual

Page 198

169

Chapter 7 Timer/Counter Units

7

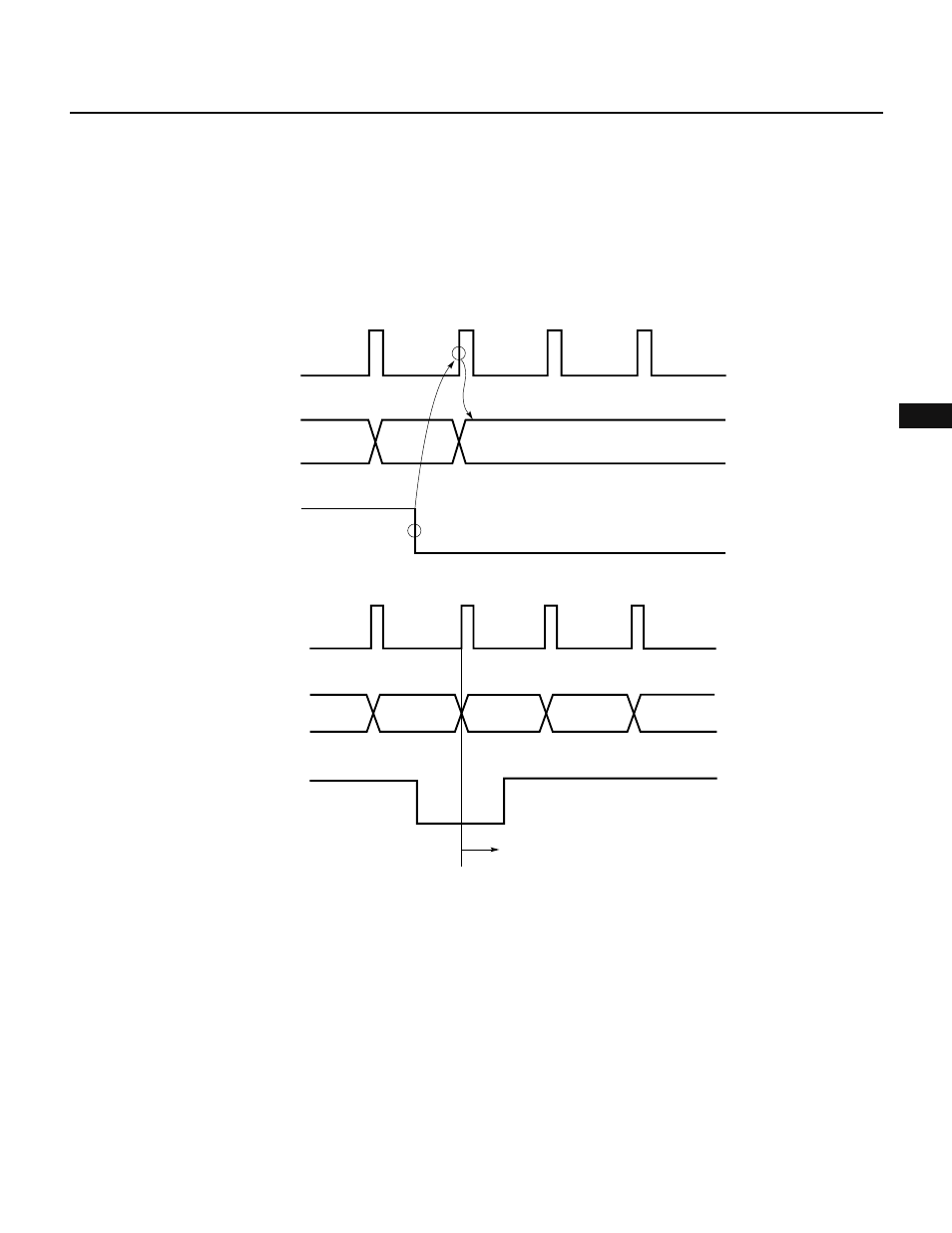

TM2 can also be cleared by software when the CE2 bit of the timer control register (TMC1) is reset to 0.

Similarly, clear operation is performed by the count clock pulse following the resetting of CE2 bit to 0. If the

CE2 bit is set to 1 before TM2 is reset to 0 by the resetting of the CE2 bit to 0 (that is, before the first count clock

pulse is applied after the CE2 bit is reset to 0), two operations are simultaneously performed: one operation

is an operation to clear TM2 to 0, and the other operation is a count operation starting with the counting of

0.

Fig. 7-74 Clear Operation When the CE2 Bit Is Reset to 0

(a) Basic operation

TM2

CE2

n-1

n

0

Count clock

(b) Restart after 0 is set in TM2 cleared

Count clock

TM2

CE2

n-1

n

0

0

1

When the CE2 bit is set to 1 aftr this count clock,

counting starts from 0 on the count clock input

after the CE2 bit has been set.