5 interrupt status register (ist), Chapter 12 interrupt functions – NEC PD78214 User Manual

Page 336

307

Chapter 12 Interrupt Functions

12

When a low-priority vectored interrupt is being handled, vectored interrupt requests with lower and higher

priorities are accepted for multiple-interrupt handling provided that interrupts are enabled. When a high-priority

interrupt is being handled, high-priority vectored interrupts are accepted for multiple-interrupt handling provided

that interrupts are enabled. Moreover, any interrupt requests specifying a macro service are accepted regardless

of their priority.

When the RESET signal is input, this register is set to FFFFH, thereby specifying that all interrupts be in the low-

priority group.

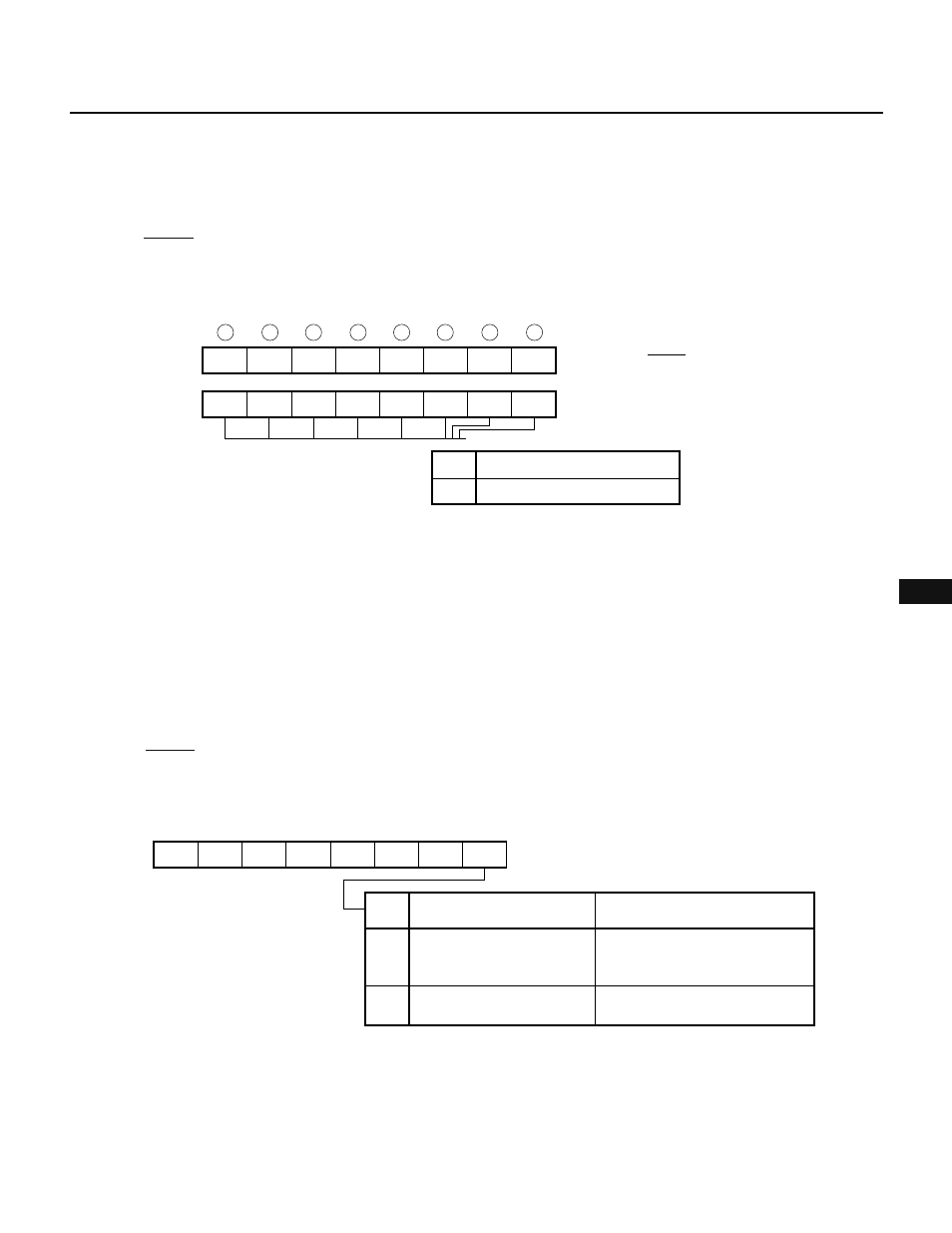

Fig. 12-6 Priority Specification Flag Register (PR0) Format

12.2.5 Interrupt Status Register (IST)

The IST register is an 8-bit register that controls multiple-interrupt handling for nonmaskable interrupt requests

(input to the NMI pin) and indicates whether a nonmaskable interrupt request has been accepted.

When a nonmaskable interrupt is being handled, another nonmaskable interrupt request may occur. In such a

case, the nonmaskable interrupt request is accepted if the NMIS bit is 0; it is not accepted if the NMIS bit is 1.

The NMIS bit is set to 1 when a nonmaskable interrupt request is accepted. It is reset to 0, when a return (execution

of the RETI instruction) from the interrupt handling for the nonmaskable interrupt request occurs.

Both an 8-bit manipulation instruction and bit manipulation instruction can be used to read data from and write

data to the IST register. The NMIS flag is set to 1 when a nonmaskable interrupt is accepted. It is reset to 0 by the

RETI instruction. Fig. 12-7 shows the format of the IST register.

When the RESET signal is input, the register is reset to 00H.

Fig. 12-7 Interrupt Status Register (IST) Format

Multiple interrupt processing by

nonmaskable interrupt request

NMIS

Enabled

Execution exits from nonmaskable

interrupt processing or nonmaskable

interrupt request is not accepted.

0

Disabled

Nonmaskable interrupt request is

accepted or being processed.

1

0

7

0

6

0

5

0

4

0

3

0

2

0

1

NMIS

0

IST

Accepting status for

nonmaskable interrupt request

CSIPR STPR

SRPR SERPR CPR20

PPR5

PPR4

CPR21

PR0H

High priority

0

Low priority

1

CPR11 CPR10 CPR01 CPR00

PPR3

PPR2

PPR1

PPR0

PR0L

(FFFFH when RESET signal is input)

Priority specification flags

7

6

5

4

3

2

1

0