4 operation of 16-bit timer 0 (tm0) – NEC PD78214 User Manual

Page 143

114

µ

PD78214 Sub-Series

7.1.4 Operation of 16-Bit Timer 0 (TM0)

(1) Basic operation

The 16-bit timer/counter performs count operation by counting up with a count clock of f

CLK

/8.

When the RESET signal is applied, TM0 is cleared to 0000H, and count operation stops.

Bit 3 (CE0) of timer control register 0 (TMC0) is used to enable/disable count operation. When the CE0 bit is

reset to 1 by software, TM0 is cleared to 0000H by the first count clock pulse, then count-up operation starts.

When the CE0 bit is reset to 0, TM0 is cleared to 0000H by the next count clock pulse, then capture operation

and coincide with signal generation stop.

If the CE0 bit is set to 1 when the CE0 bit is already set to 1, TM0 is not cleared, but continues count operation.

If the count clock is applied when the value of TM0 is FFFFH, TM0 is set to 0000H. At this time, OVF0 is set

to send the overflow signal to the output control circuit. OVF0 can be cleared only by software. Count

operation continues.

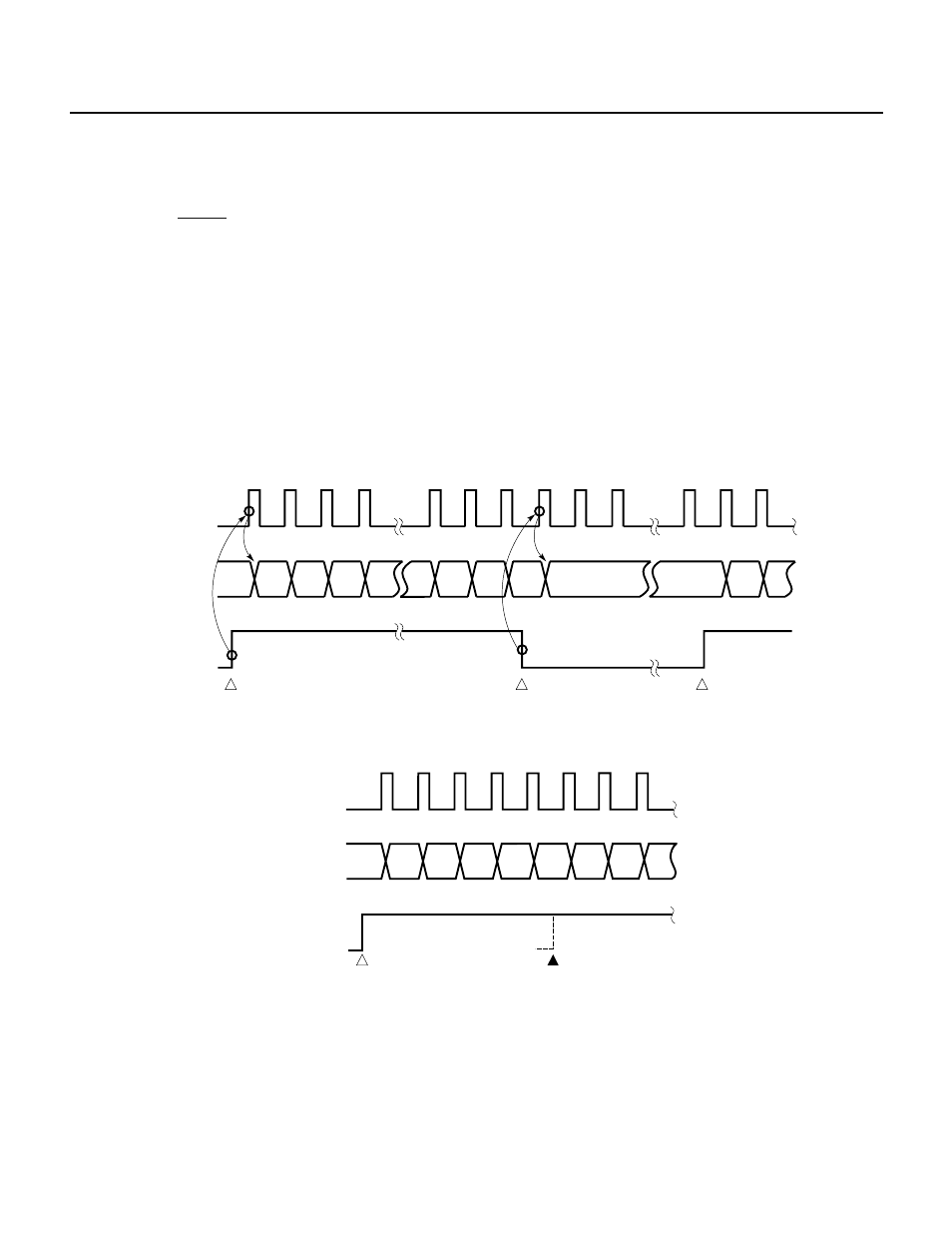

Fig. 7-6 Basic Operation of 16-Bit Timer 0 (TM0)

(a) Count start

→ count stop → count start

CE0

TM0

Count starts

Count stops

CE0

←1

CE0

←0

Count starts

CE0

←1

0H

1H

2H

FFH 100H

101H

0H

1H

0H

0H

Count clock

f

CLK

/8

(b) When the CE0 bit is set to 1 again after count operation starts

Count starts

CE0

←1

CE0

←1

Count clock

f

CLK

/8

CE0

TM0

Rewriting

0H

0H

1H

2H

3H

4H

5H

6H