6 one-shot timer function, Chapter 7 timer/counter units – NEC PD78214 User Manual

Page 204

175

Chapter 7 Timer/Counter Units

7

7.3.6 One-Shot Timer Function

Eight-bit timer/counter 2 has an operation mode in which the full-count (FFH) is reached as the result of count

operation.

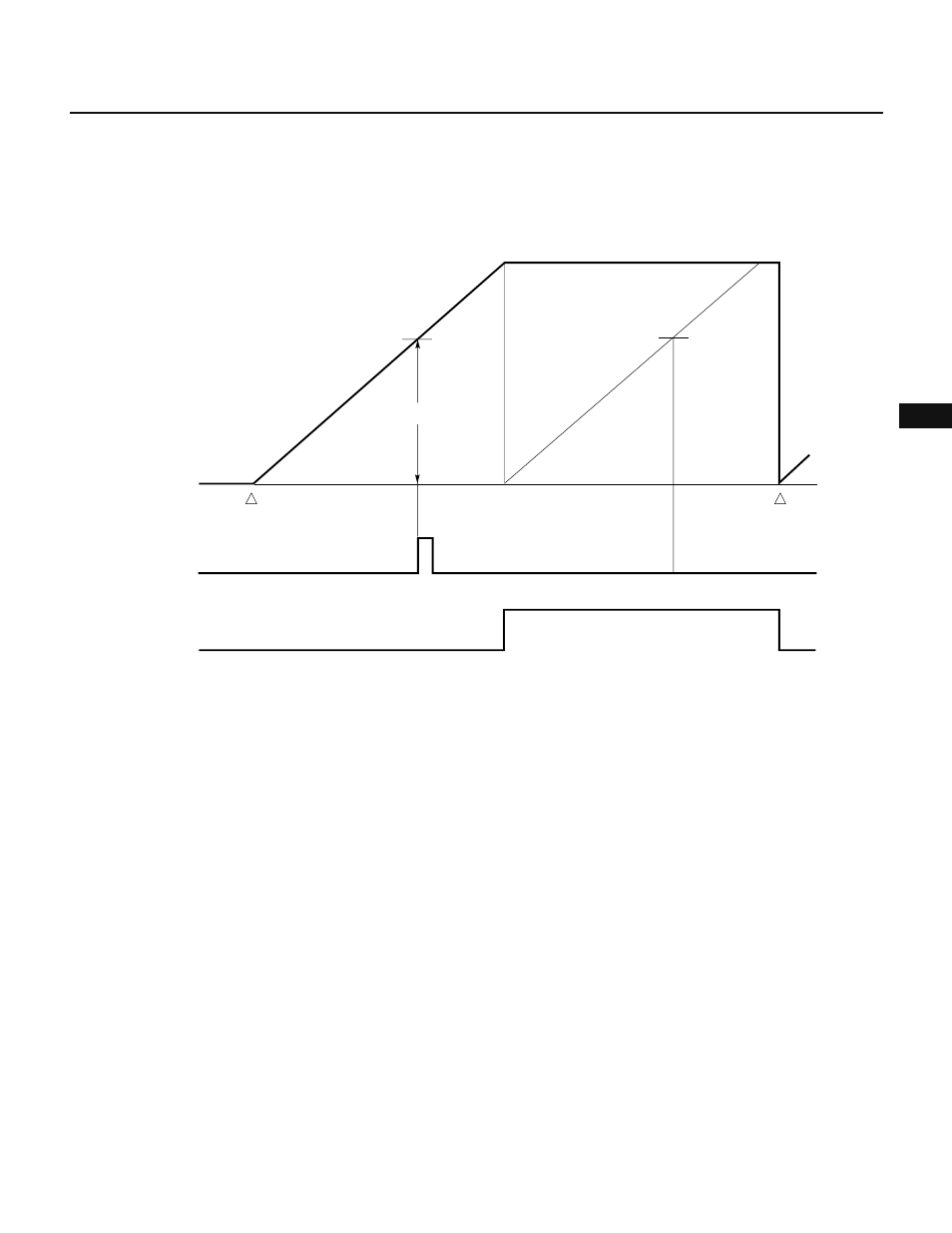

Fig. 7-79 One-Shot Timer Operation

As shown in Fig. 7-79, a one-shot interrupt is generated when the value (00H-FFH) set in the CR20 or CR21 register

coincides with the value of TM2.

The one-shot timer operation mode can be specified by setting bit 5 (CMD2) of timer control register 1 (TMC1) to

1 by software.

The count operation of TM2 is controlled using the CE2 bit of the TMC1 register as in the case of basic operation.

When the CE2 bit is set to 1 by software, TM2 is cleared to 00H by the first count clock pulse, then count-up operation

starts.

When the value of TM2 reaches FFH (full-count) as the result of count operation, bit 6 (OVF2) of the TMC1 register

is set to 1, and TM2 stops its count operation with the count value of FFH held.

From the count stop state, one-shot timer operation can be started again by resetting the OVF2 bit to 0 by

software. When the OVF2 bit is reset to 0, TM2 is cleared to 00H by the next count clock pulse, then count-up

operation restarts.

When the CE2 bit is reset to 0 by software during TM2 count operation, TM2 is cleared to 00H by the next count

clock pulse, and count operation stops. If the CE2 bit is set to 1 by software when the CE2 bit is already set to 1,

TM2 count operation is not affected.

0H

INTC21

OVF2

OVF2

←0

Count starts

CE2

←1

TM2

count value

Value of CR21

Cleared

FFH