Chapter 10 clock synchronous serial interface – NEC PD78214 User Manual

Page 304

275

Chapter 10 Clock Synchronous Serial Interface

10

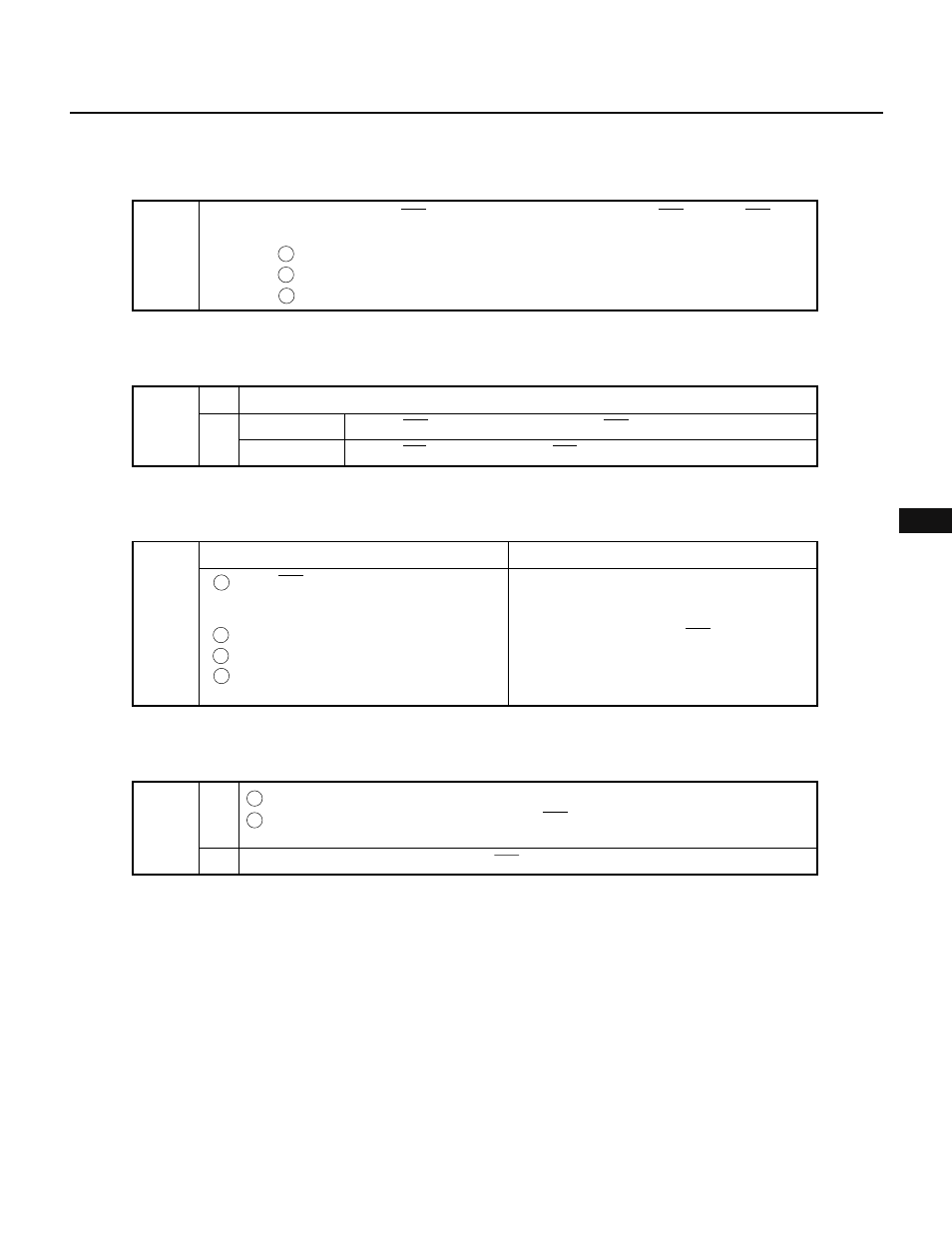

Fig. 10-11 Format of SBIC Register (2/2)

Remarks

(R)

: Read-only

(W)

: Write-only

(R/W): Read/write

★

Acknowledge trigger bit (W)

Acknowledge enable bit (R/W)

Acknowledge detection flag (R)

Busy enable bit (R/W)

1

ACKT

Do not set this bit to 1 before serial transfer is completed.

2

ACKT cannot be cleared by software.

3

Set ACKT when ACKE = 0.

When this bit is set after transfer, ACK is output in synchronization with the next SCK. After the ACK signal

is output, this bit is automatically cleared to 0.

1

ACKD

When SCK falls first time after releasing busy

after the transfer start instruction has been

executed

2

When RESET signal is input

3

CTXE = CRXE = 0

Clearing condition (ACKD = 0)

Setting condition (ACKD = 1)

When acknowledge signal (ACK) is detected

4

When bus release is detected (in slave mode

only)

Cautions:

ACKE

Disables automatic output of acknowledge signal

Before transfer

After transfer

0

Outputs ACK in synchronization with the 9th SCK

Outputs ACK in synchronization with SCK immediately after set instruction execution

1

BSYE

Outputs busy signal in synchronization with SCK falling after acknowledge signal

0

1

1

Disables automatic output of busy signal

2

Stops busy signal output in synchronization with SCK falling immediately after clear instruction

execution