5 usable devices, Usable devices, External device setup manual – IDEC High Performance Series User Manual

Page 210

Chapter 2

192

External Device Setup Manual

4.5

Usable Devices

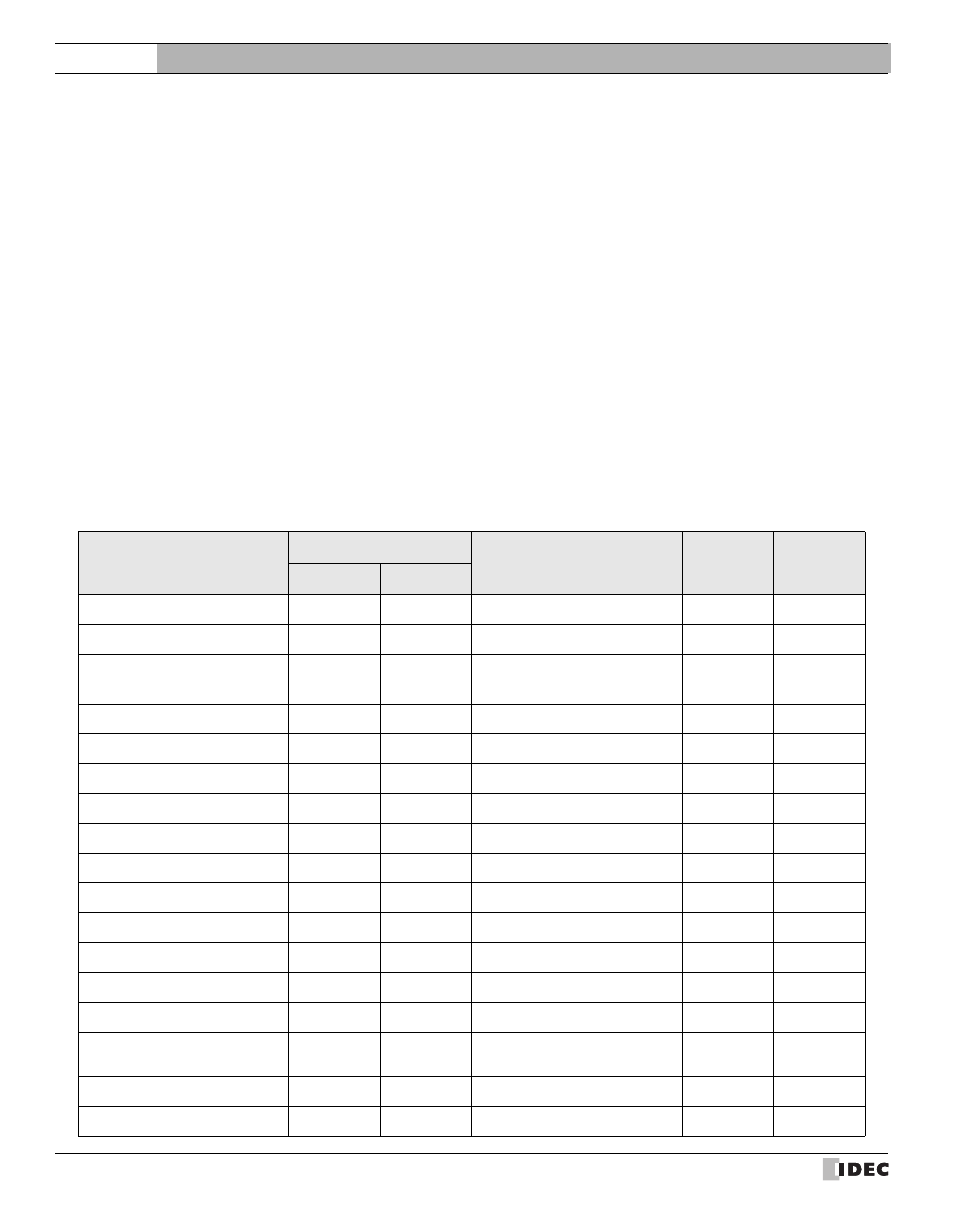

The types of compatible devices and their ranges are shown below. Device address selection for the MicroLogix1200, SLC 500 and

PLC-5 CPU’s are is done using File No., Element No., Bit No. etc., with an appropriate delimiter. But the WindO/I-NV2 address

selection is done without the delimiter. The MICRO/I address specification syntax (address specification rules) is explained below.

Follow the syntax below when performing address selections using WindO/I-NV2 software.

MICRO/I support the following device types and range.

WindO/I-NV2 supports the device address format as same as MicroLogix, SLC 500, PLC-5 programming software along with the

standard device address format of WindO/I-NV2.

•

Standard device address format of WindO/I-NV2

File Number, Element and Bit Number are separated by some delimiters in device address format of Allen-Bradley’s software.

However, standard device address format of WindO/I-NV2 does not contain delimiters.

It is remove some delimiters from Allen-Bradley’s device address format.

•

Allen-Bradley device address format

This device address format is same as the device address format of Allen-Bradley’s software.

(Some part of the format is deferent. Refer to the following.)

4.5.1

MicroLogix, SLC 500 (Full Duplex)

Bit Device

Device Name

Device Symbol

Address Range

Read

/Write

Address

Gradual

MICRO/I

PLC

Output

O

O

0 - 1625515

R

10

*1

Input

I

I

0 - 1625515

R

10

Binary

B

B

300000 - 325515,

900000 - 25525515

R/W

10

*2

Timer Enable Bit

TEN

T(EN)

4000 - 4255, 9000 - 255255

R

10

*3

Timer Timing Bit

TTT

T(TT)

4000 - 4255, 9000 - 255255

R

10

Timer Done Bit

TDN

T(DN)

4000 - 4255, 9000 - 255255

R

10

Counter Up Enable Bit

CCU

C(CU)

5000 - 5255, 9000 - 255255

R

10

Counter Down Enable Bit

CCD

C(CD)

5000 - 5255, 9000 - 255255

R

10

Counter Done Bit

CDN

C(DN)

5000 - 5255, 9000 - 255255

R

10

Counter Overflow Bit

COV

C(OV)

5000 - 5255, 9000 - 255255

R

10

Counter Underflow Bit

CUN

C(UN)

5000 - 5255, 9000 - 255255

R

10

Counter Update Accumulator

CUA

C(UA)

5000 - 5255, 9000 - 255255

R

10

Control Enable Bit

REN

R(EN)

6000 - 6255, 9000 - 255255

R

10

Control Queue Bit

REU

R(EU)

6000 - 6255, 9000 - 255255

R

10

Control Asynchronous Bit

Done Bit

RDN

R(DN)

6000 - 6255, 9000 - 255255

R

10

Control Synchronous Done Bit

REM

R(EM)

6000 - 6255, 9000 - 255255

R

10

Control Error Bit

RER

E(ER)

6000 - 6255, 9000 - 255255

R

10