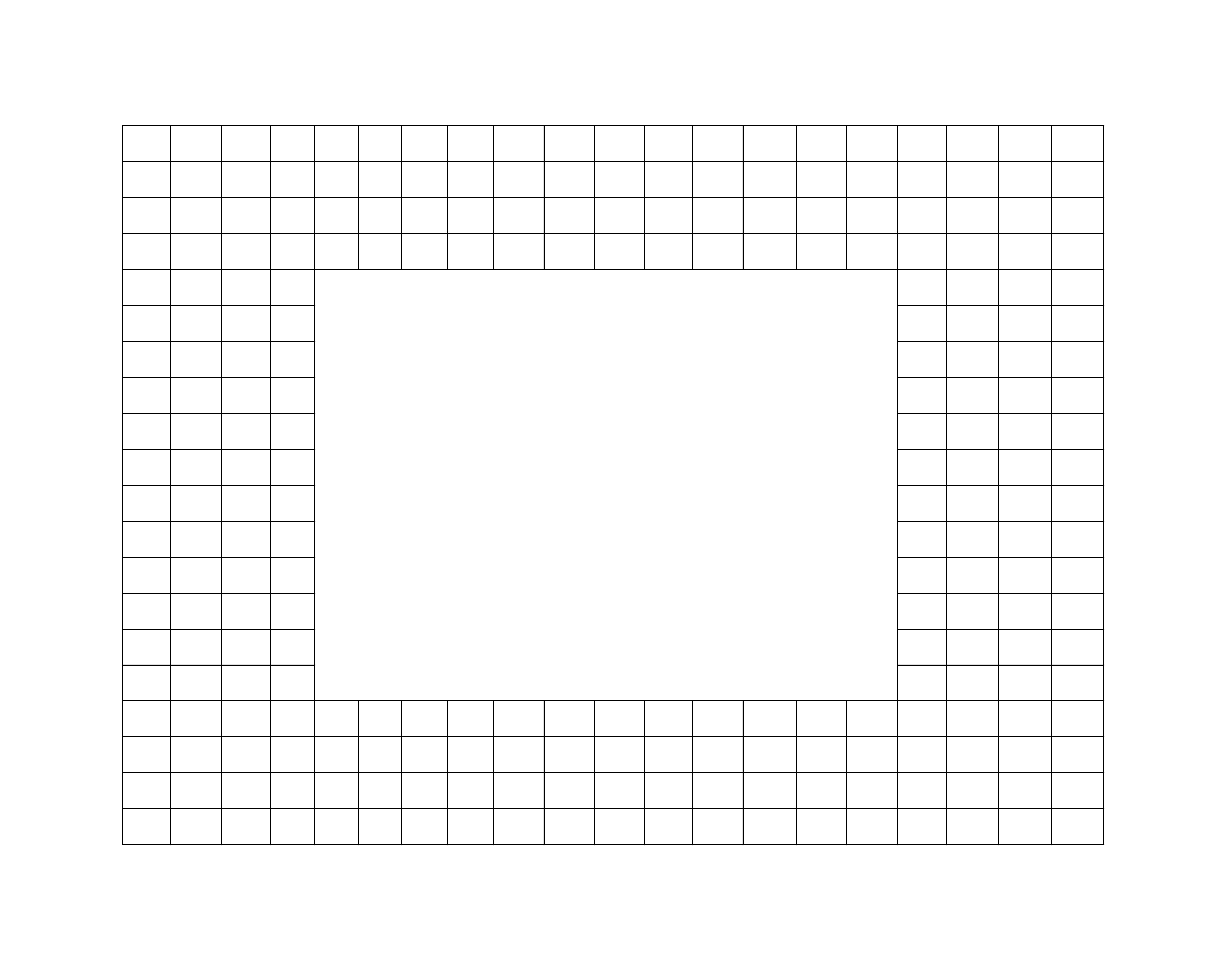

Lsi53c876 256-ball bga diagram (top view), Figure 3.2 – Avago Technologies LSI53C876E User Manual

Page 75

3-3

Figure 3.2

LSI53C876 256-Ball BGA Diagram (Top View)

)

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

VSS

AD27

AD30

REQ/

RST/

MCE/

MWE/

B_IGS

B_SDIR13

VDD

A_SDIR13 A_SDIR0

A_SDIR4

A_SDIR7

A_SD12/

A_SDP1/

A_SD2

A_SD3

A_SD6/

A_SD7/

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

AD26

AD28

VDD-IO

AD31

GNT/

INTA/

MOE/_TO

MAS1/

VDD

A_SDIR12 A_SDIR15 A_SDIR1

A_SDIR5 A_DIRP0/1

A_SD13/

A_SD0/

A_SD4/

A_SD5

A_SDP0/

A_SATN/

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

AD24

VSS

NC

AD29

VDD-C

VSS-C

INTB/

MAS0/

B_SDIR12 B_SDIR15 A_SDIR14 A_SDIR2

A_SDIR6

VDD

A_SD15/

A_SD1/

NC

NC

A_SBSY/

A_SRST/

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

C_BE3/

AD25

NC

VSS

VSS

NC

CLK

VSS

B_TGS

B_SDIR14

NC

A_SDIR3

VSS

A_SD14/

NC

NC

VSS

NC

A_SMSG/

A_SC_D/

E1

E2

E3

E4

E17

E18

E19

E20

AD23

IDSEL

VDD-IO

NC

A_SACK/

A_SSEL/

A_SREQ/

A_SD9/

F1

F2

F3

F4

F17

F18

F19

F20

AD21

AD22

VSS

NC

NC

A_SI_O/

A_SD10/

VDD

G1

G2

G3

G4

G17

G18

G19

G20

AD19

VDD-IO

AD20

NC

A_SD8/

A_SD11/

A_SDIR8

A_SDIR9

H1

H2

H3

H4

H17

H18

H19

H20

AD17

AD18

VSS

VSS

VSS

A_SDIR10 A_SDIR11 A_BSYDIR

J1

J2

J3

J4

J17

J18

J19

J20

FRAME/

C_BE2/

VSS

AD16

VDD-C

A_RSTDIR

VSS-C

A_SELDIR

K1

K2

K3

K4

K17

K18

K19

K20

VSS

VDD-IO

IRDY/

NC

A_IGS

A_TGS

A_DIFSEN

VDD

L1

L2

L3

L4

L17

L18

L19

L20

TRDY/

DEVSEL/

NC

STOP/

NC

B_SDIR1

B_SDIR2

B_SDIR0

M1

M2

M3

M4

M17

M18

M19

M20

VSS

PERR/

VDD-IO

SERR/

B_SDIR6

B_SDIR5

B_SDIR4

B_SDIR3

N1

N2

N3

N4

N17

N18

N19

N20

PAR

C_BE1/

VSS

VSS

VSS

VDD

B_DIRP0/1

B_SDIR7

P1

P2

P3

P4

P17

P18

P19

P20

AD15

AD14

VDD-IO

AD11

B_SD0/

B_SD14/

B_SD13/

B_SD12/

R1

R2

R3

R4

R17

R18

R19

R20

AD13

AD12

AD10

NC

NC

B_SD1/

B_SDP1/

B_SD15/

T1

T2

T3

T4

T17

T18

T19

T20

VSS

AD9

AD8

NC

NC

B_SD4/

B_SD3/

B_SD2/

U1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

R16

R17

R18

R19

R20

VSS

VDD-IO

NC

VSS

VSS

NC

VDD-C

VSS

MAD7

NC

B_GPIO0 B_GPIO4

VSS

VDD

NC

B_SC_D/

VSS

NC

B_SD7/

B_SD5

V1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

R16

R17

R18

R19

R20

C_BE0/

AD7

NC

AD2

TCK

VDD-C

VSS-C

A_GPIO2

VDD

MAD4

MAD0

B_GPIO3 B_RSTDIR

B_SDIR9

B_SD11/

B_SD8/

B_SSEL/

NC

B_SDP0/

B_SD6/

W1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

R16

R17

R18

R19

R20

AD6

VSS

AD4

VDD-IO

TDI

SCLK

A_GPIO0 A_GPIO3

MAD6

NC

MAD1

B_GPIO2 B_SELDIR B_SDIR11

B_SDIR8

B_SD10/

B_SI_O/

B_SMSO/

B_SACK/

b-SATN/

Y1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

R16

R17

R18

R19

R20

AD5

AD3

AD1

AD0

TMS

TESTIN/ A_GPIO1 A_GPIO4

MAD5

MAD3

MAD2

B_GPIO1

VDD

B_BSYDIR B_SDIR10 B_DIFSEN

B_SD9/

B_SREQ/

B_SRST/

B_SBSY/