Table 2.8 mode c serial eeprom data format, Mode c serial eeprom data format – Avago Technologies LSI53C876E User Manual

Page 69

Serial EEPROM Interface

2-47

The format of the serial EEPROM data is defined in

. If the

EEPROM is not present, or the checksum fails, the

and

registers read back all zeros. At power-up or hard

reset, only five bytes are loaded into the chip from locations 0xFB

through 0xFF.

The

and

registers are read only, in

accordance with the PCI specification, with a default value of all zeros.

Before implementing Mode C, contact LSI Logic for additional

information.

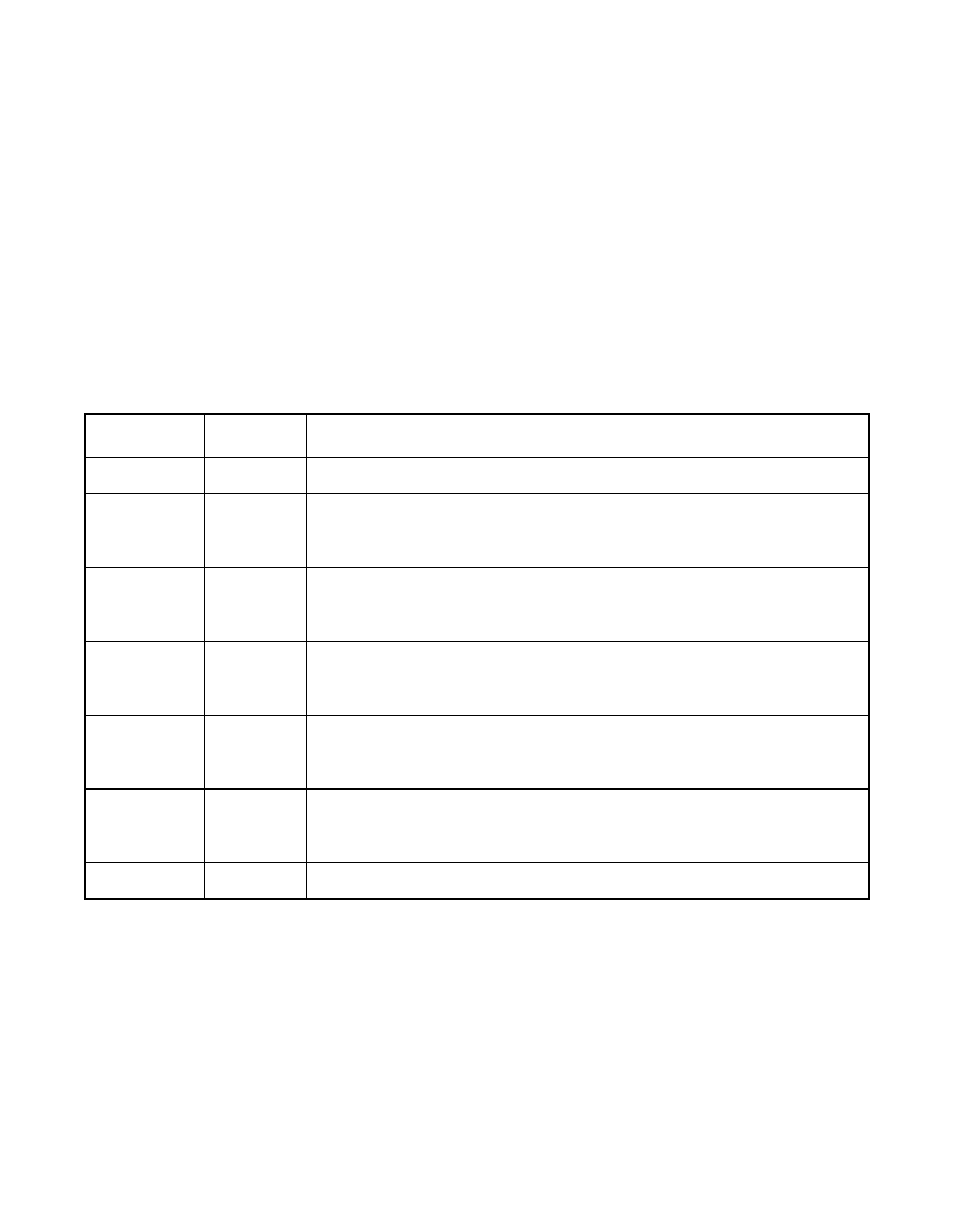

Table 2.8

Mode C Serial EEPROM Data Format

Byte

Name

Description

0x00–0xFA

UD0

User Data.

0xFB

SVID(0)

, LSB. This byte is loaded into the least significant

byte of the

register in the appropriate PCI

configuration space at chip power-up or hard reset.

0xFC

SVID(1)

, MSB. This byte is loaded into the most significant

byte of the

register in the appropriate PCI

configuration space at chip power-up or hard reset.

0xFD

SID(0)

, LSB. This byte is loaded into the least significant byte of

the

register in the appropriate PCI configuration space at

chip power-up or hard reset.

0xFE

SID(1)

, MSB. This byte is loaded into the most significant byte

of the

register in the appropriate PCI configuration space

at chip power-up or hard reset.

0xFF

CKSUM

Checksum. This 8-bit checksum is formed by adding, bytewise, each

byte contained in locations 0x00–0x03 to the seed value 0x55, and then

taking the 2’s complement of the result.

0x100–EOM

UD

User Data.