Register: 0x46, Register: 0x47 – Avago Technologies LSI53C876E User Manual

Page 176

4-82

Registers

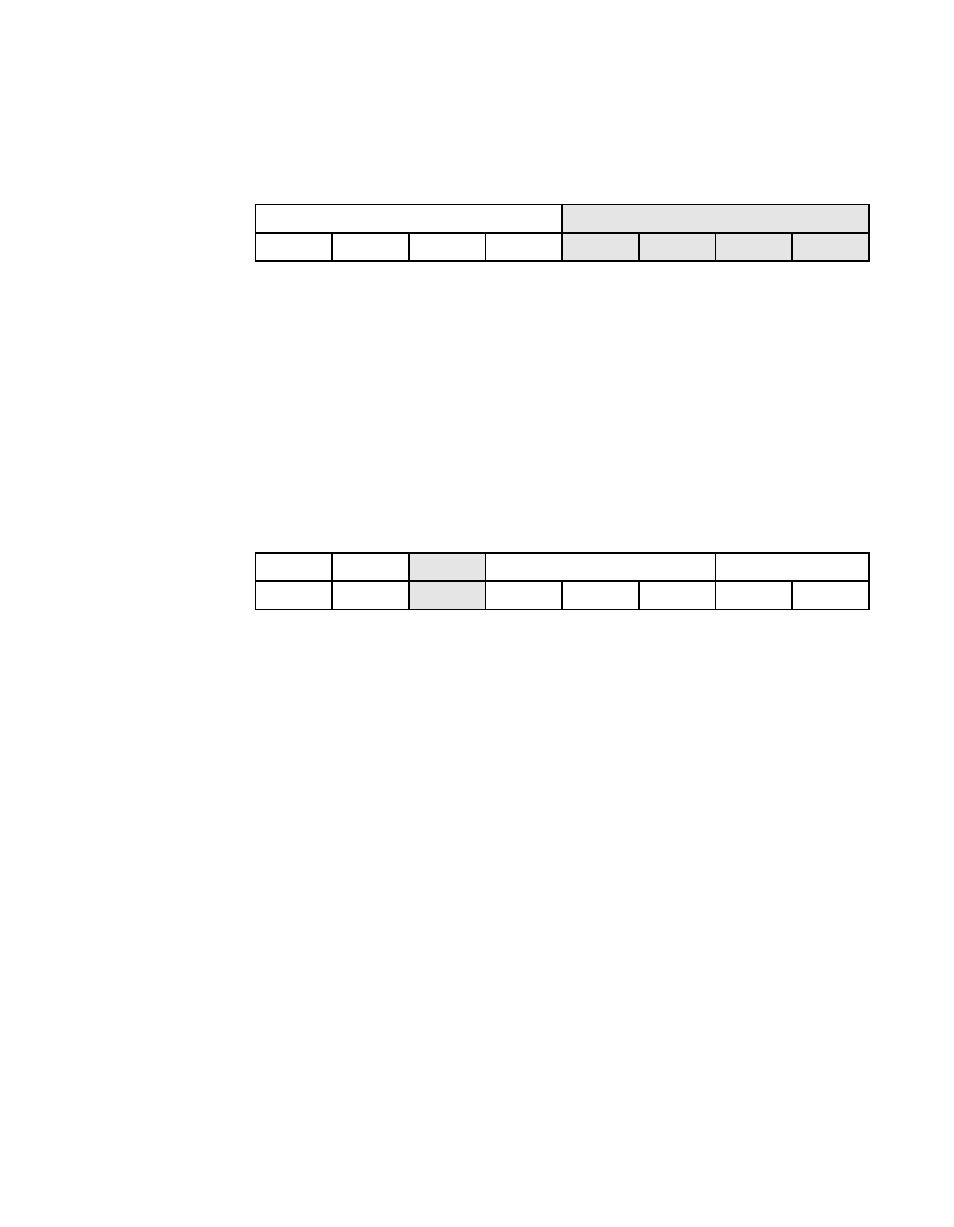

Register: 0x46

Memory Access Control (MACNTL)

Read/Write

TYP[3:0]

Chip Type

[7:4]

These bits identify the chip type for software purposes.

This technical manual applies to devices that have these

bits set to 0x70.

R

Reserved

[3:0]

Register: 0x47

General Purpose Pin Control (GPCNTL)

Read/Write

This register determines if the pins controlled by the

are inputs or outputs. Bits [4:0] in GPCNTL correspond to bits

[4:0] in the GPREG register. When the bits are enabled as inputs, an

internal pull-up is also enabled. If either SCSI function

register has a GPIO pin set as an output, the pin

is enabled as an output. If both the SCSI function GPREG registers

define a single GPIO pin as an output, the results are indeterminate.

ME

Master Enable

7

The internal bus master signal is presented on GPIO1 if

this bit is set, regardless of the state of bit 1 (GPIO1_EN).

FE

Fetch Enable

6

The internal opcode fetch signal is presented on GPIO0

if this bit is set, regardless of the state of bit 0

(GPIO0_EN).

7

4

3

0

TYP[3:0]

R

0

1

1

1

x

x

x

x

7

6

5

4

2

1

0

ME

FE

R

GPIO[4:2]

GPIO[1:0]

0

0

x

0

1

1

1

1