Scsi chip id (scid), Scsi chip id, Scid) – Avago Technologies LSI53C876E User Manual

Page 126: Register: 0x04

4-32

Registers

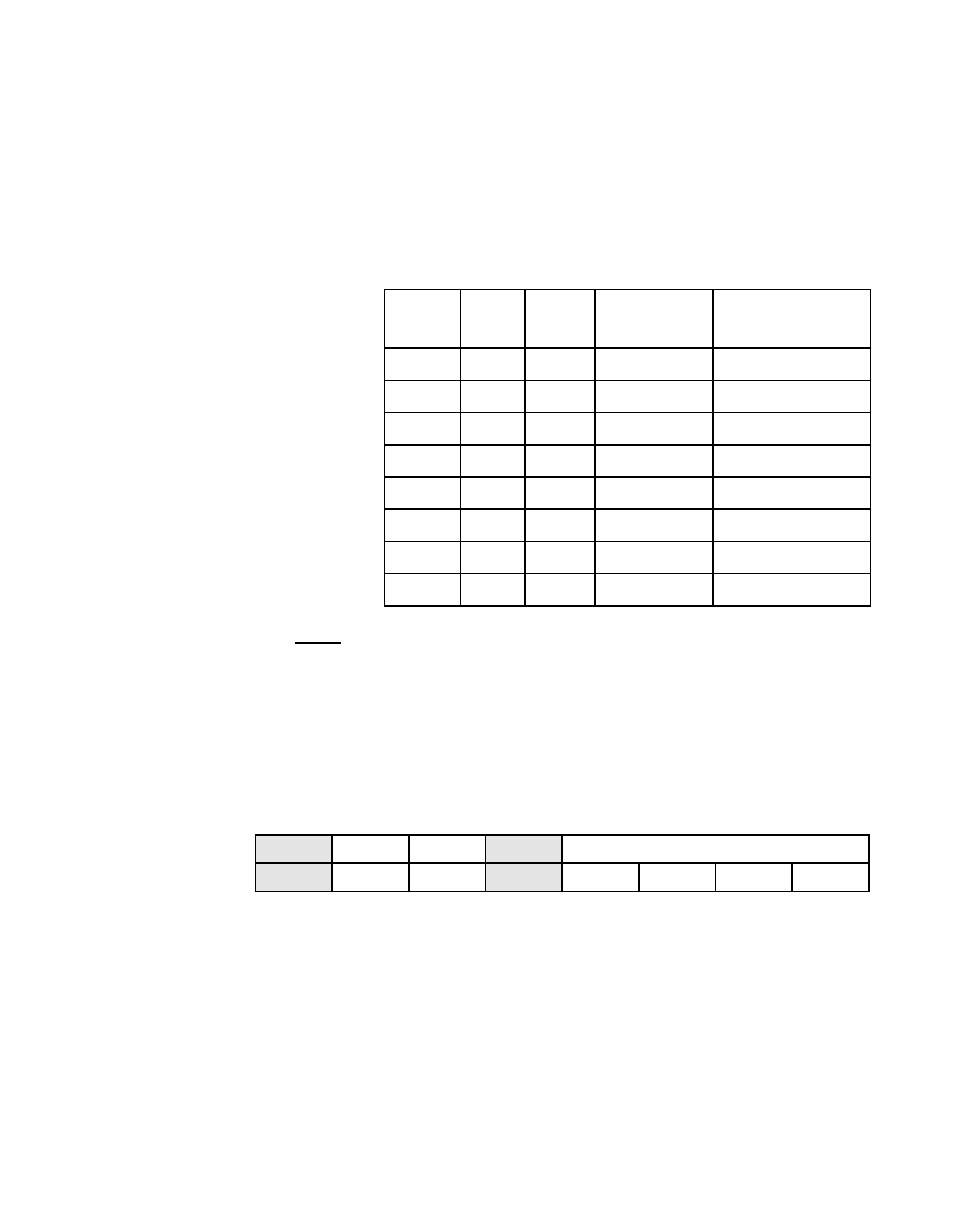

Clock Conversion Factor

[2:0]

These bits select a factor by which the frequency of

SCLK is divided before being presented to the SCSI core.

The synchronous portion of the SCSI core can be run at

a different clock rate for fast SCSI, using the

Synchronous Clock Conversion Factor bits. The bit

encoding is displayed in the table below. All other

combinations are reserved.

Note:

It is important that these bits are set to the proper values

to guarantee that the LSI53C876 meets the SCSI timings

as defined by the ANSI specification.

Register: 0x04

SCSI Chip ID (SCID)

Read/Write

R

Reserved

7

RRE

Enable Response to Reselection

6

When this bit is set, the LSI53C876 SCSI function is

enabled to respond to bus-initiated reselection at the chip

ID in the

and

SCF2

CCF2

SCF1

CCF1

SCF0

CCF0

Factor

Frequency

SCSI Clock (MHz)

0

0

0

SCLK/3

50.01–75.0

0

0

1

SCLK/1

16.67–25.0

0

1

0

SCLK/1.5

25.01–37.5

0

1

1

SCLK/2

37.51–50.0

1

0

0

SCLK/3

50.01–75.0

1

0

1

SCLK/4

75.01-80.00

1

1

0

SCLK/6

120

1

1

1

SCLK/8

160

7

6

5

4

3

0

R

RRE

SRE

R

ENC[3:0]

x

0

0

x

0

0

0

0

- MGA-725M4 (4 pages)

- MGA-71543 (4 pages)

- MGA-71543 (3 pages)

- MGA-82563 (6 pages)

- 3ware 9690SA-8I (Channel) (380 pages)

- 3ware SAS 9750-8i (48 pages)

- 3ware 9690SA-8I (Channel) (138 pages)

- 3ware 9550SXU-8LP (Channel) (149 pages)

- 3ware SAS 9750-8i (29 pages)

- 3ware 9550SXU-8LP (Channel) (40 pages)

- 3ware 9650SE-8LPML (Channel) (45 pages)

- 3ware 9690SA-8I (Channel) (27 pages)

- 3ware 9690SA-8I (Channel) (361 pages)

- 6160 SAS Switch (2 pages)

- MegaRAID SAS 9361-8i (13 pages)

- MegaRAID SAS 9266-8i (12 pages)

- MegaRAID SAS 9380-8e (43 pages)

- Cache Protection for RAID Controller Cards (139 pages)

- Cache Protection for RAID Controller Cards (13 pages)

- MegaRAID SAS 9271-8iCC (13 pages)

- MegaRAID SAS 9285-8ecv (80 pages)

- MegaRAID SAS 9285-8ecv (92 pages)

- MegaRAID SAS 9266-8i (20 pages)

- MegaRAID SAS 9271-8iCC (26 pages)

- MegaRAID SafeStore Software (502 pages)

- MegaRAID SAS 0260CV-4i (64 pages)

- MegaRAID SAS 0260CV-4i (49 pages)

- MegaRAID SAS 9271-8i (8 pages)

- MegaRAID SAS 0260CV-4i (72 pages)

- MegaRAID SAS 9361-8i (7 pages)

- MegaRAID SAS 9341-8i (8 pages)

- MegaRAID SAS 9380-4i4e (7 pages)

- MegaRAID SAS 9380-8e (7 pages)

- MegaRAID SAS 9240-8i (4 pages)

- MegaRAID SAS 0260CV-4i (28 pages)

- MegaRAID SAS 9260-16i (12 pages)

- MegaRAID SAS 9280-24i4e (14 pages)

- MegaRAID SAS 9280-24i4e (16 pages)

- MegaRAID SAS 9260-8i (4 pages)

- MegaRAID SafeStore Software (8 pages)

- MegaRAID SAS 9280-8e (22 pages)

- MegaRAID SAS 9261-8i (4 pages)

- MegaRAID SAS 9285-8e (12 pages)

- MegaRAID SAS 9280-16i4e (12 pages)

- MegaRAID SAS 9280-4i4e (4 pages)