2 pci bus commands and functions supported, Table 2.1 pci bus commands and encoding types, Pci bus commands and functions supported – Avago Technologies LSI53C876E User Manual

Page 26: Pci bus commands and encoding types

2-4

Functional Description

I/O Space – The PCI specification defines I/O space as a contiguous

32-bit I/O address that is shared by all system resources, including the

LSI53C876. The

Base Address Register Zero (I/O)

register determines

which 256-byte I/O area this device occupies.

Memory Space – The PCI specification defines memory space as a

contiguous 32-bit memory address that is shared by all system

resources, including the LSI53C876. The

register determines which 256-byte memory area this device

occupies. Each SCSI function uses a 4 K SCRIPT RAM memory space.

The

Base Address Register Two (Memory)

register determines the

4 Kbyte memory area occupied by SCRIPTS RAM.

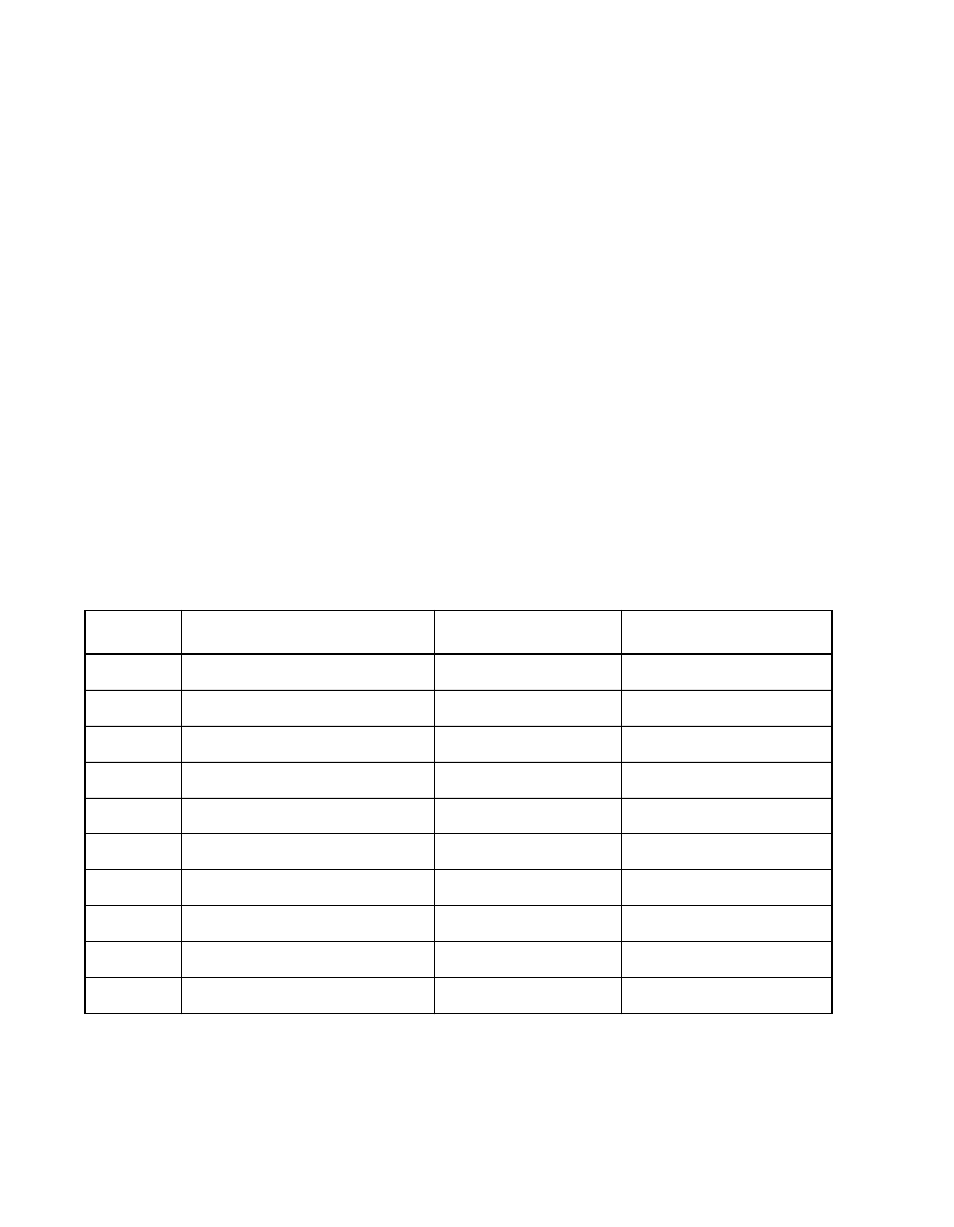

2.1.2 PCI Bus Commands and Functions Supported

Bus commands indicate to the target the type of transaction the master

is requesting. Bus commands are encoded on the C_BE/[3:0] lines

during the address phase. PCI bus commands and encoding types

appear in

.

Table 2.1

PCI Bus Commands and Encoding Types

C_BE[3:0] Command Type

Supported as Master Supported as Slave

0b0000

Interrupt Acknowledge

No

No

0b0001

Special Cycle

No

No

0b0010

I/O Read

Yes

Yes

0b0011

I/O Write

Yes

Yes

0b0100

Reserved

N/A

N/A

0b0101

Reserved

N/A

N/A

0b0110

Memory Read

Yes

Yes

0b0111

Memory Write

Yes

Yes

0b1000

Reserved

N/A

N/A

0b1001

Reserved

N/A

N/A