4 mode d operation, 5 power management, Table 2.9 power states – Avago Technologies LSI53C876E User Manual

Page 70: Mode d operation, Power management, Power states, Section 2.5, “power management

2-48

Functional Description

2.4.4 Mode D Operation

No pull-down on MAD6, and a 4.7 K pull-down on MAD7. The

and the

are automatically set to

0x1000. This allows the OEM to have a non-zero value in the registers

without requiring a serial EEPROM on the board.

2.5 Power Management

The LSI53C876E complies with the PCI Bus Power Management

Interface Specification, Revision 1.0. The PCI Function Power States D0,

D1, D2, and D3 are defined in that specification.

D0 is the maximum powered state, and D3 is the minimum powered

state. Power state D3 is further categorized as D3hot or D3cold.

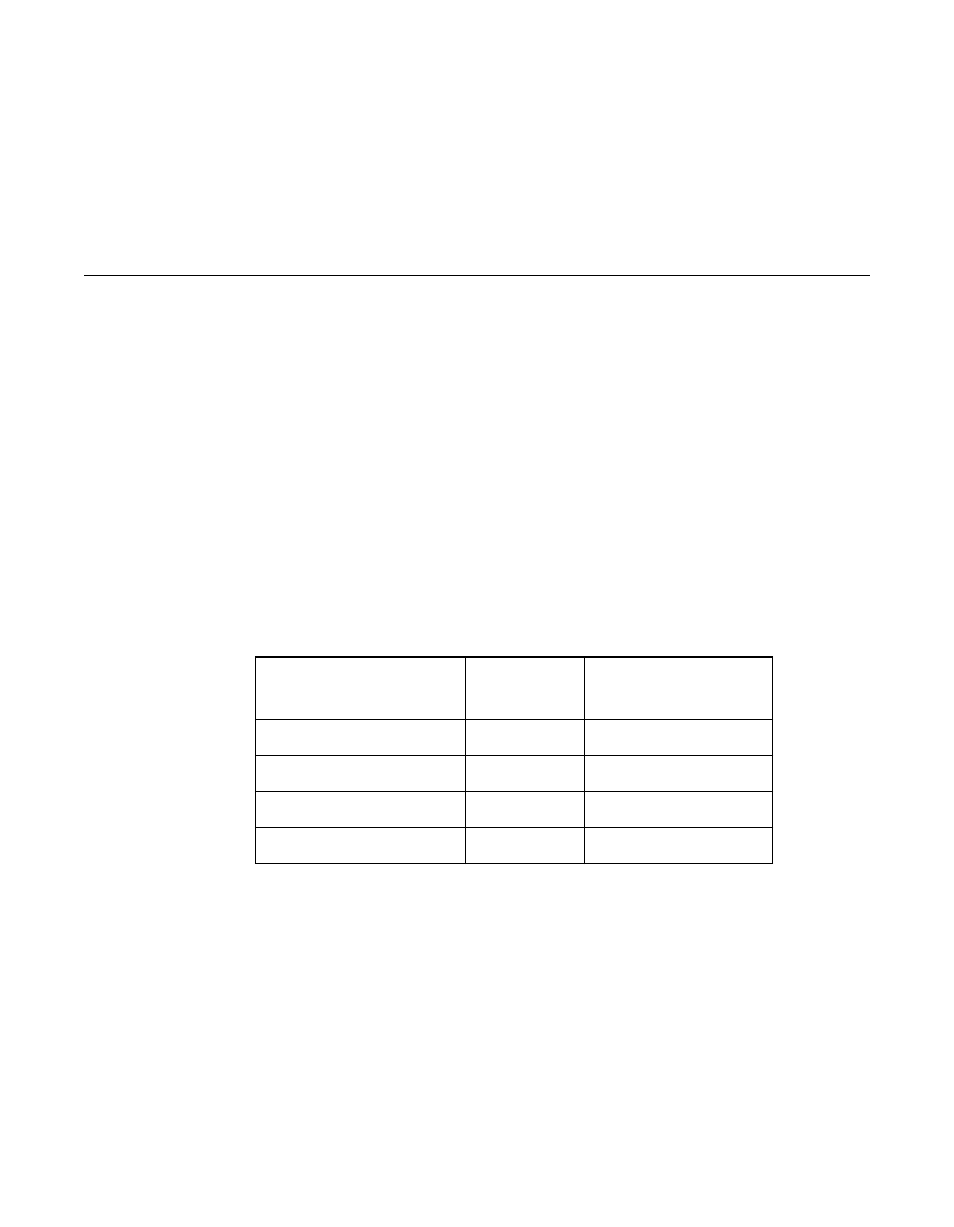

The LSI53C876E power states shown in

are independently

controlled through two power state bits that are located in the PCI

Configuration Space register 0x44.

Although the PCI Bus Power Management Interface Specification does

not allow power state transitions D2 to D1, D3 to D2, or D3 to D1, the

LSI53C876E hardware places no restriction on transitions between

power states.

As the device transitions from one power level to a lower one, the

attributes that occur from the higher power state level are carried over

into the lower power state level. For example, D1 disables the SCSI CLK.

Therefore, D2 will include this attribute as well as the attributes defined

Table 2.9

Power States

Configuration Register

0x44 Bits [1:0]

Power State

Function

00

D0

Maximum Power

01

D1

Disables SCSI clock

10

D2

Coma Mode

11

D3

Minimum Power