Scsi test one (stest1), Register: 0x4d – Avago Technologies LSI53C876E User Manual

Page 182

4-88

Registers

SCSI function, as an initiator, is waiting for the target to

request data transfers. If the LSI53C876 SCSI function is

a target, then the initiator has sent the offset number of

acknowledges.

SOM

SCSI Synchronous Offset Maximum

0

This bit indicates that the current synchronous SREQ/,

SACK/ offset is the maximum specified by bits [3:0] in the

register. This bit is not latched

and may change at any time. It is used in low level

synchronous SCSI operations. When this bit is set, the

LSI53C876 SCSI function, as a target, is waiting for the

initiator to acknowledge the data transfers. If the

LSI53C876 SCSI function is an initiator, then the target

has sent the offset number of requests.

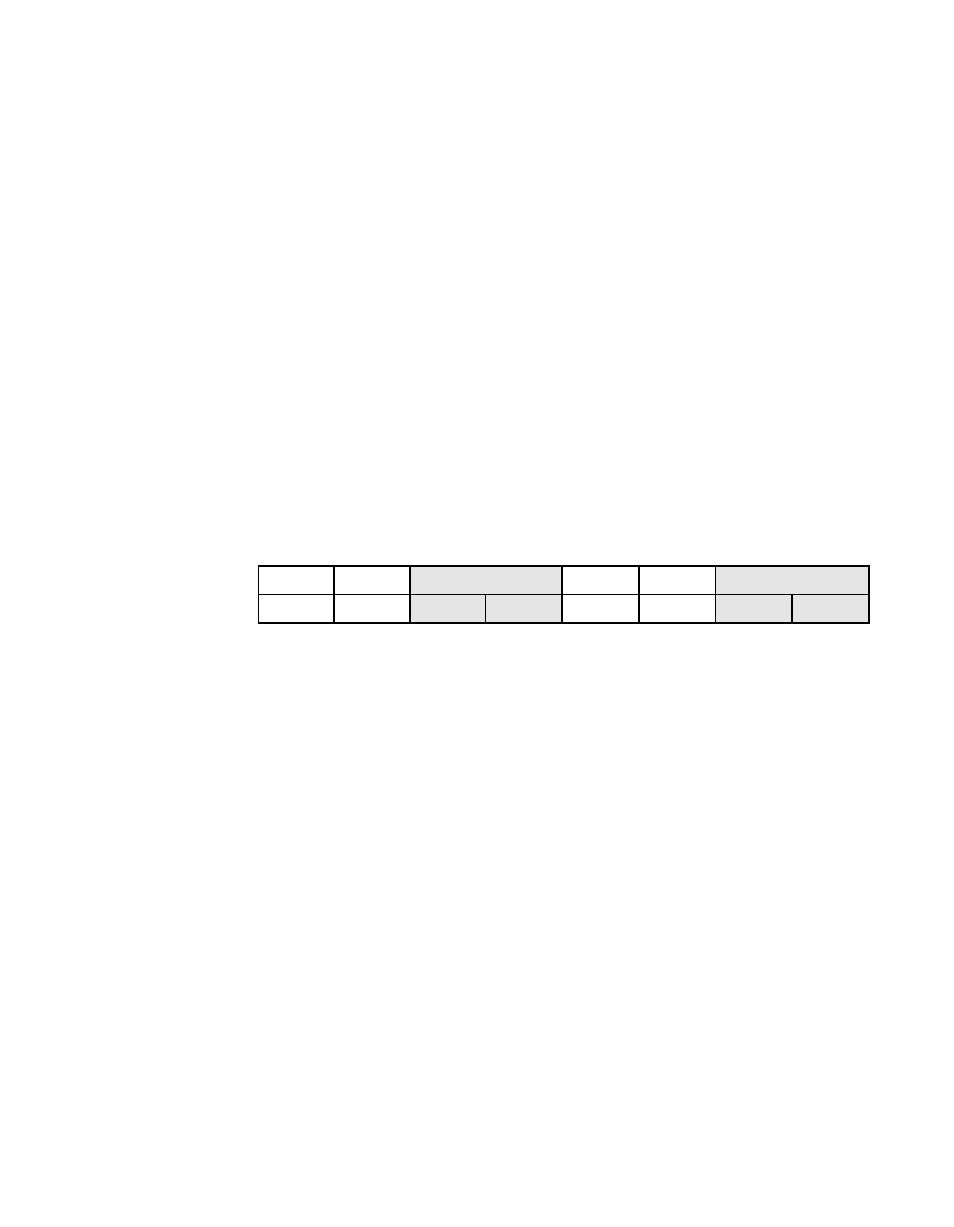

Register: 0x4D

SCSI Test One (STEST1)

Read/Write

SCLK

SCSI Clock

7

When set, this bit disables the external SCLK (SCSI

Clock) pin, and the chip uses the PCI clock as the

internal SCSI clock. If a transfer rate of 10 Mbytes/s (or

20 Mbytes/s on a wide SCSI bus) is desired on the SCSI

bus, this bit must be cleared and a 40 MHz external

SCLK must be provided.

ISO

SCSI Isolation Mode

6

This bit allows the LSI53C876 SCSI function to put the

SCSI bidirectional and input pins into a low power mode

when the SCSI bus is not in use. When this bit is set, the

SCSI bus inputs are logically isolated from the SCSI bus.

R

Reserved

[5:4]

DBLEN

SCLK Doubler Enable

3

This bit, when reset, powers down the internal clock

doubler circuit, which doubles the SCLK 40 MHz clock to

an internal 80 MHz SCSI clock required for Wide Ultra

7

6

5

4

3

2

1

0

SCLK

SISO

R

DBLEN

DBLSEL

R

0

0

x

x

0

0

x

x