Bits used for parity control and generation, Table 2.2 – Avago Technologies LSI53C876E User Manual

Page 40

2-18

Functional Description

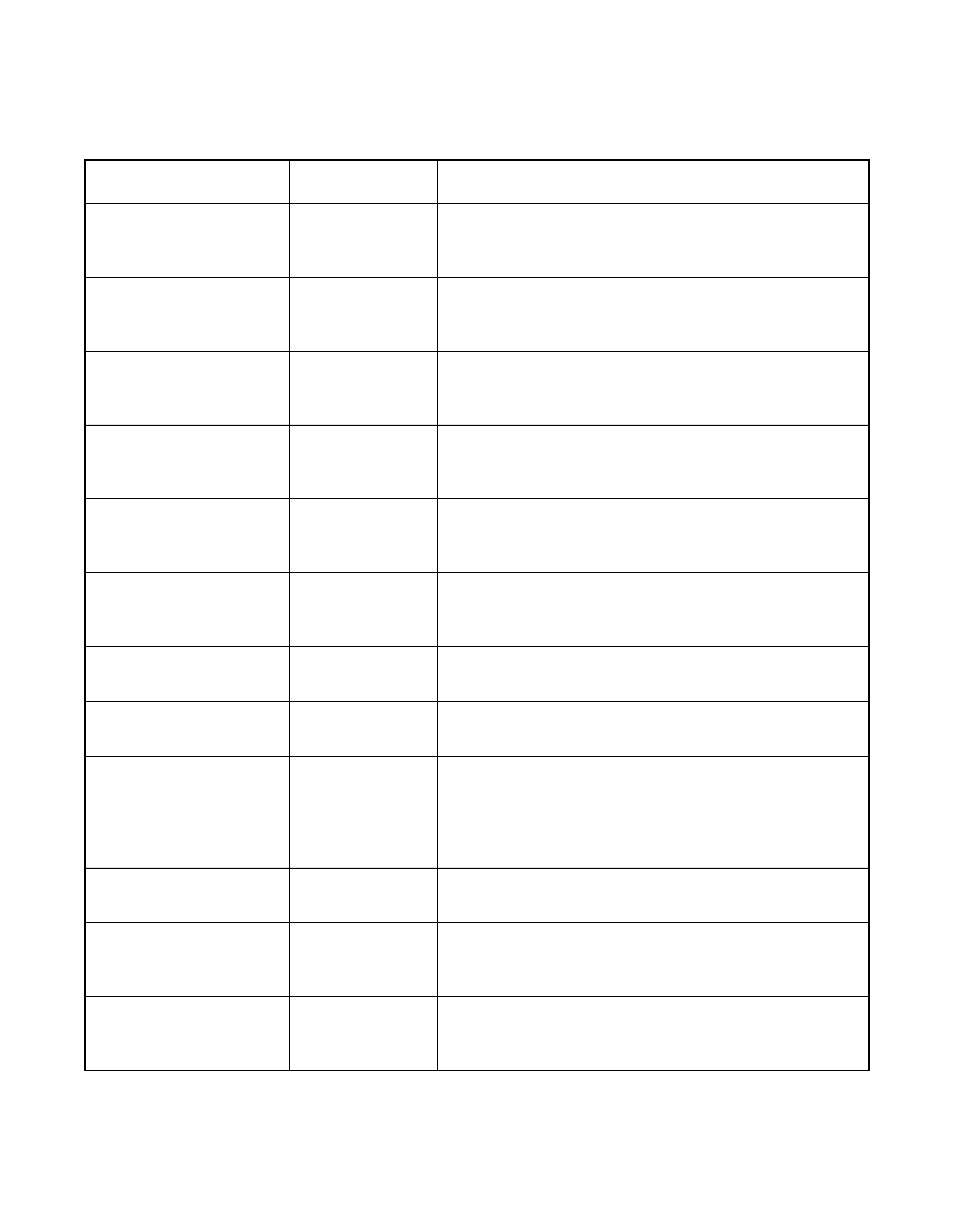

Table 2.2

Bits Used for Parity Control and Generation

BIt Name

Location

Description

Assert SATN/ on Parity

Errors

,

Bit 1

Causes the LSI53C876 to automatically assert SATN/

when it detects a parity error while operating as an

initiator.

Enable Parity Checking

,

Bit 3

Enables the LSI53C876 to check for parity errors. The

LSI53C876 checks for odd parity.

Assert Even SCSI Parity

Bit 2

Determines the SCSI parity sense generated by the

LSI53C876 to the SCSI bus.

Disable Halt on SATN/ or

a Parity Error (Target

Mode Only)

Bit 5

Causes the LSI53C876 not to halt operations when a

parity error is detected in target mode.

Enable Parity Error

Interrupt

SCSI Interrupt

Enable Zero

(SIEN0)

, Bit 0

Determines whether the LSI53C876 generates an

interrupt when it detects a SCSI parity error.

Parity Error

SCSI Interrupt

Status Zero

(SIST0)

, Bit 0

This status bit is set whenever the LSI53C876 detects

a parity error on the SCSI bus.

Status of SCSI Parity

Signal

, Bit 0

This status bit represents the active HIGH current state

of the SCSI SDP0 parity signal.

SCSI SDP1 Signal

, Bit 0

This bit represents the active HIGH current state of the

SCSI SDP1 parity signal.

Latched SCSI Parity

, Bit 3

and

,

Bit 3

These bits reflect the SCSI odd parity signal

corresponding to the data latched into the

register.

Master Parity Error

Enable

, Bit 3

Enables parity checking during master data phases.

Master Data Parity Error

, Bit 6

Set when the LSI53C876, as a PCI master, detects a

target device signaling a parity error during a data

phase.

Master Data Parity Error

Interrupt Enable

Bit 6

By clearing this bit, a Master Data Parity Error does not

cause assertion of INTA/ (or INTB/), but the status bit

is set in the

register.