Avalon-mm-to-pci express address translation – Altera Arria V Hard IP for PCI Express User Manual

Page 94

6–20

Chapter 6: IP Core Architecture

Avalon-MM Bridge TLPs

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

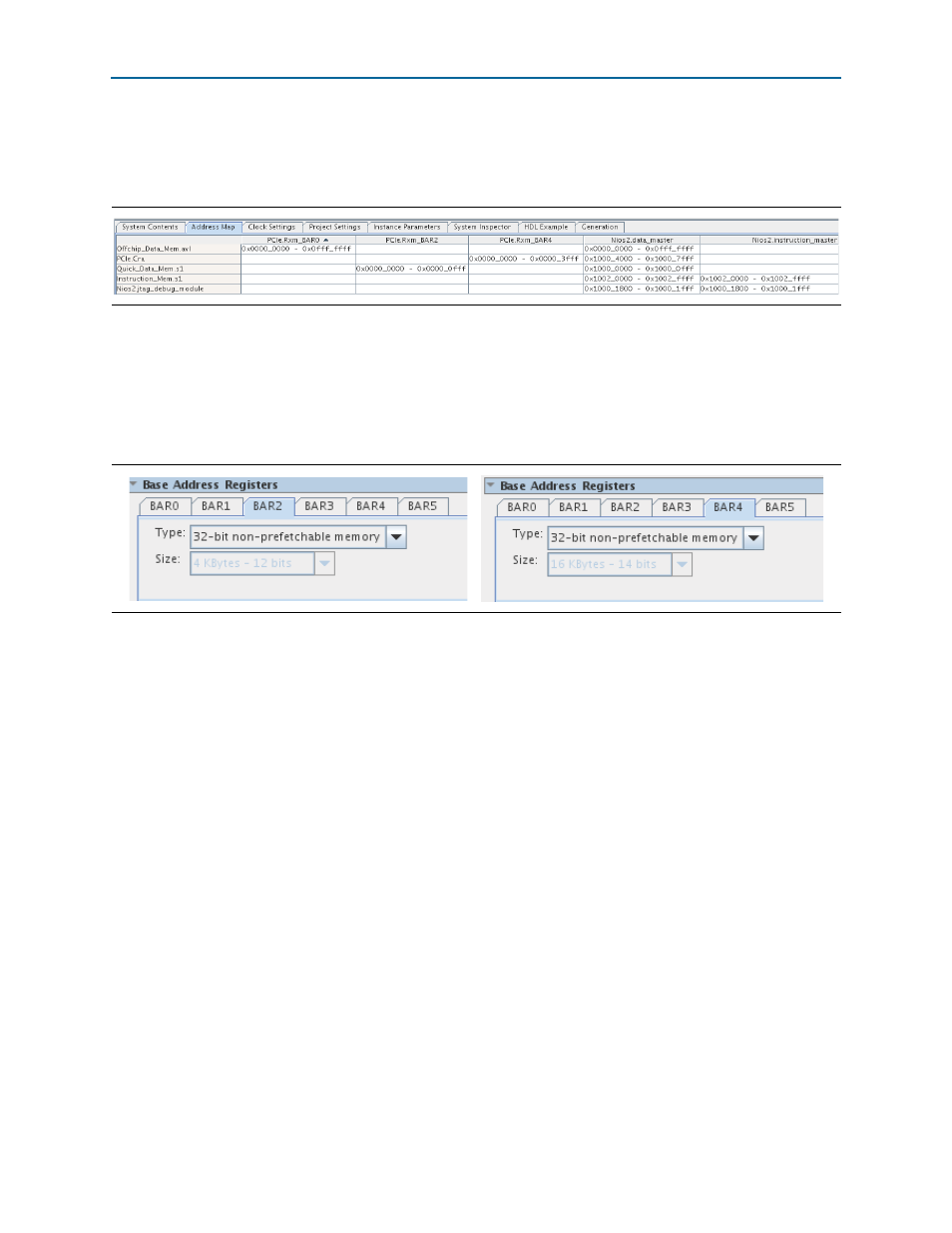

This design is consuming 1.25GB of PCIe address space when only 276 MBytes are

actually required. The solution is to edit the address map to place the base address of

each BAR at 0x0000_0000.

Figure 6–10

illustrates the optimized address map.

h

For more information about changing Qsys addresses using the Qsys address map,

refer to

in Quartus II Help.

Figure 6–11

shows the number of address bits required when the smaller memories

accessed by BAR2 and BAR4 have a base address of 0x0000_0000.

For cases where the BAR Avalon-MM RX master port connects to more than one

Avalon-MM slave, assign the base addresses of the slaves sequentially and place the

slaves in the smallest power-of-two-sized address space possible. Doing so minimizes

the system address space used by the BAR.

Avalon-MM-to-PCI Express Address Translation Algorithm

The Avalon-MM address of a received request on the TX Slave Module port is

translated to the PCI Express address before the request packet is sent to the

Transaction Layer. You can specify up to 512 address pages and sizes ranging from

4 KByte to 4 GBytes when you customize your Avalon-MM Arria V Hard IP for PCI

Express as described in

“Avalon to PCIe Address Translation Settings” on page 5–10

This address translation process proceeds by replacing the MSB bits of the

Avalon-MM address with the value from a specific translation table entry; the LSB bits

remains unchanged. The number of MSBs to be replaced is calculated based on the

total address space of the upstream PCI Express devices that the Avalon-MM Hard IP

for PCI Express can access.

The address translation table contains up to 512 possible address translation entries

that you can configure. Each entry corresponds to a base address of the PCI Express

memory segment of a specific size. The segment size of each entry must be identical.

The total size of all the memory segments is used to determine the number of address

MSB bits to be replaced. In addition, each entry has a 2-bit field,

Sp[1:0]

, that

Figure 6–10. Optimized Address Map

Figure 6–11. Reduced Address Bits for BAR2 and BAR4