Altera Arria V Hard IP for PCI Express User Manual

Page 115

Chapter 7: IP Core Interfaces

7–17

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

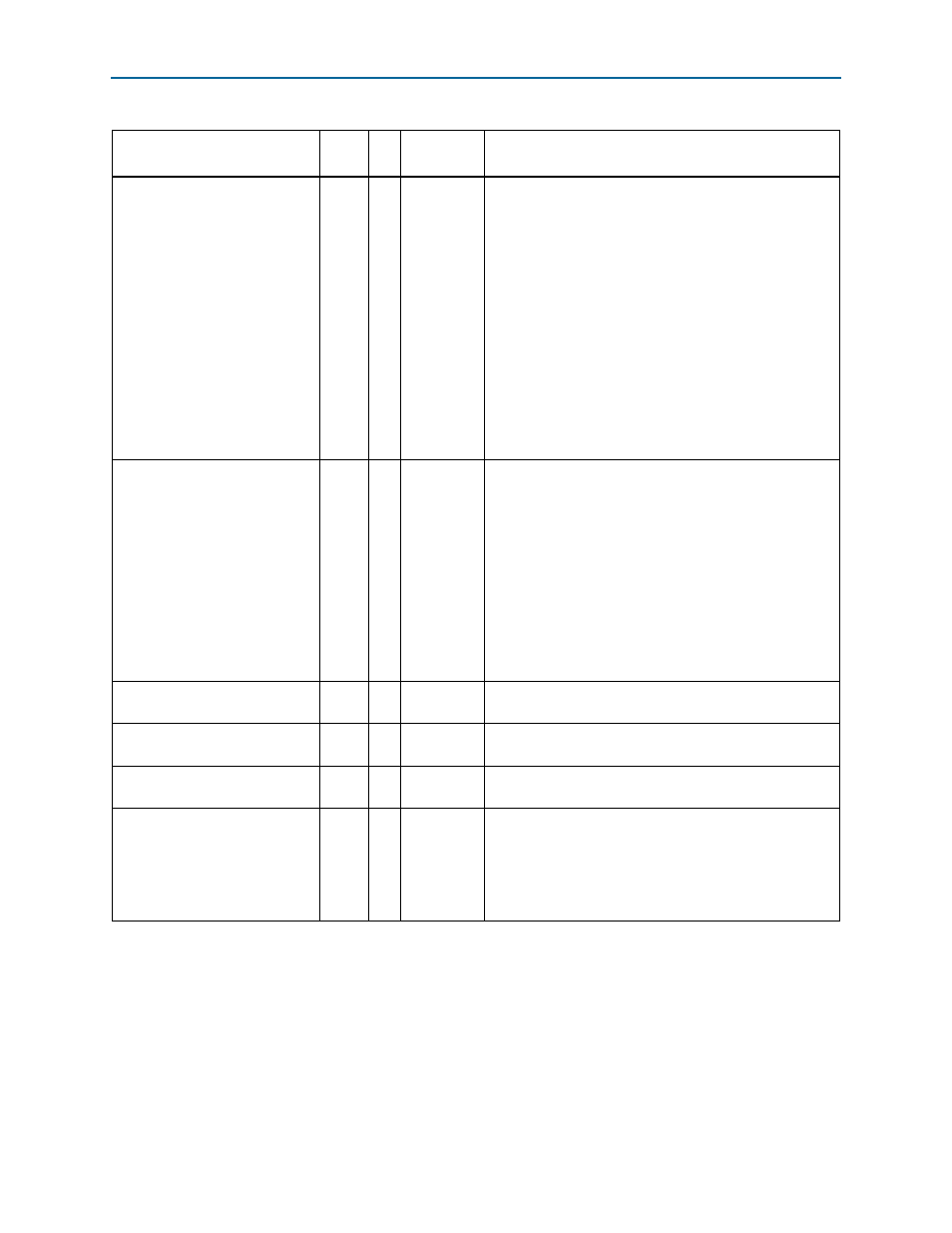

tx_cred_fchipcons

6

O

component

specific

Asserted for 1 cycle each time the Hard IP consumes a

credit. The 6 bits of this vector correspond to the following

6 types of credit types:

■

[5]: posted headers

■

[4]: posted data

■

[3]: non-posted header

■

[2]: non-posted data

■

[1]: completion header

■

[0]: completion data

During a single cycle, the Hard IP can consume either a

single header credit or both a header and a data credit. The

Application Layer must keep track of credits consumed by

the Application Layer logic.

tx_cred_fc_infinite

6

O

component

specific

When asserted, indicates that the corresponding credit

type has infinite credits available and does not need to

calculate credit limits. The 6 bits of this vector correspond

to the following 6 types of credit types:

■

[5]: posted headers

■

[4]: posted data

■

[3]: non-posted header

■

[2]: non-posted data

■

[1]: completion header

■

[0]: completion data

tx_cred_hdrfccp

8

O

component

specific

Header credit limit for transmission of completions. Each

credit is 20 bytes.

tx_cred_hdrfcnp

8

O

component

specific

Header limit for transmission of non-posted requests. Each

credit is 20 bytes.

tx_cred_hdrfcp

8

O

component

specific

Header credit limit for transmission of posted writes. Each

credit is 20 bytes.

ko_cpl_spc_header

8

O

component

specific

ko_cpl_spc_header

is a static signal that indicates the

total number of completion headers that can be stored in

the RX buffer. The Application Layer can use this signal to

build circuitry to prevent RX buffer overflow for completion

headers. Endpoints must advertise infinite space for

completion headers; however, RX buffer space is finite.

Table 7–4. 64- or 128-Bit Avalon-ST TX Datapath (Part 3 of 4)

Signal

Width

Dir

Avalon-ST

Type

Description