Coreclkout_hip, Pld_clk, Coreclkout_hip –6 pld_clk –6 – Altera Arria V Hard IP for PCI Express User Manual

Page 186: Refer to, For a

9–6

Chapter 9: Reset and Clocks

Clocks

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

For designs that transition between Gen1 and Gen2,

pclk

can be turned off for the

entire 1 ms timeout assigned for the PHY to change the clock rate; however,

pclk

should be stable before the 1 ms timeout expires.

The CDC module implements the asynchronous clock domain crossing between the

PHY/MAC

pclk

domain and the Data Link Layer

coreclk

domain.

coreclkout_hip

The

coreclkout_hip

signal is derived from

pclk

.

lists frequencies for

coreclkout

_hip which are a function of the link width, data rate, and the width of the

Avalon-ST bus.

The frequencies and widths specified in

operation. If the link downtrains to a lesser link width or changes to a different

maximum link rate, it maintains the frequencies it was originally configured for as

specified in

. (The Hard IP throttles the interface to achieve a lower

throughput.) If the link also downtrains from Gen2 to Gen1, it maintains the

frequencies from the original link width, for either Gen1 or Gen2.

pld_clk

This clock drives the Transaction Layer, Data Link Layer, part of the PHY/MAC

Layer, and the Application Layer. Ideally, the

pld_clk

drives all user logic in the

Application Layer, including other instances of the Arria V Hard IP for PCI Express

and memory interfaces. Using a single clock simplifies timing. You should derive the

pld_clk

clock from the

coreclkout_hip

output clock pin.

pld_clk

does not have to be

phase locked to

coreclkout_hip

because the clock domain crossing logic handles this

timing issue.

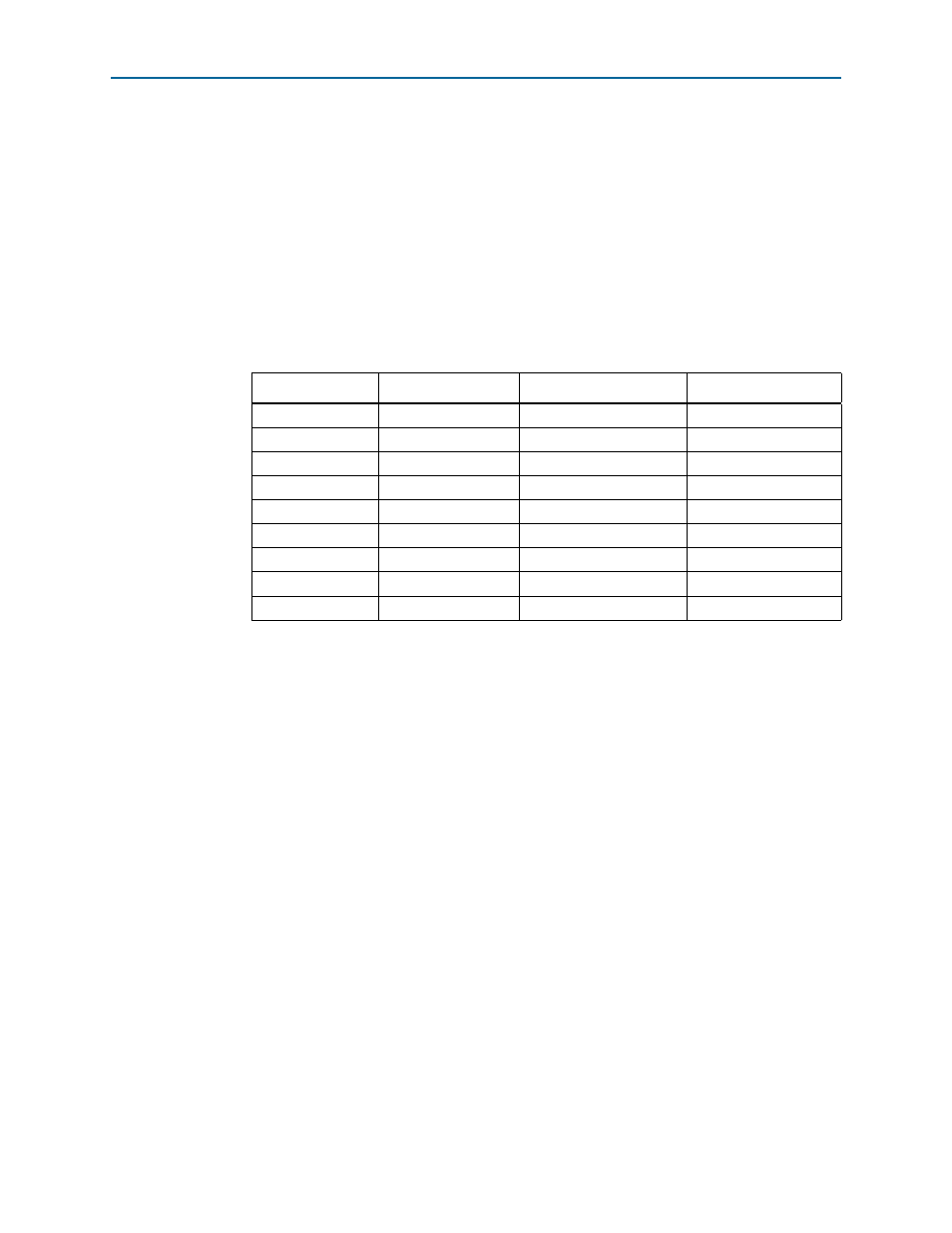

Table 9–2. coreclkout_hip Values for All Parameterizations

Link Width

Max Link Rate

Avalon Interface Width

coreclkout_hip

×1

Gen1 64

125

MHz

×1

Gen1

64

×2

Gen1

64

125 MHz

×4

Gen1 64

125

MHz

×8

Gen1

128

125 MHz

×1

Gen2

64

62.5 MHz

×1

Gen2

64

125 MHz

×2

Gen2

64

125 MHz

×4

Gen2

128

125 MHz

Note to

:

(1) This mode saves power.