Pipe interface signals, Pipe interface signals –51 – Altera Arria V Hard IP for PCI Express User Manual

Page 149

Chapter 7: IP Core Interfaces

7–51

Physical Layer Interface Signals

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

1

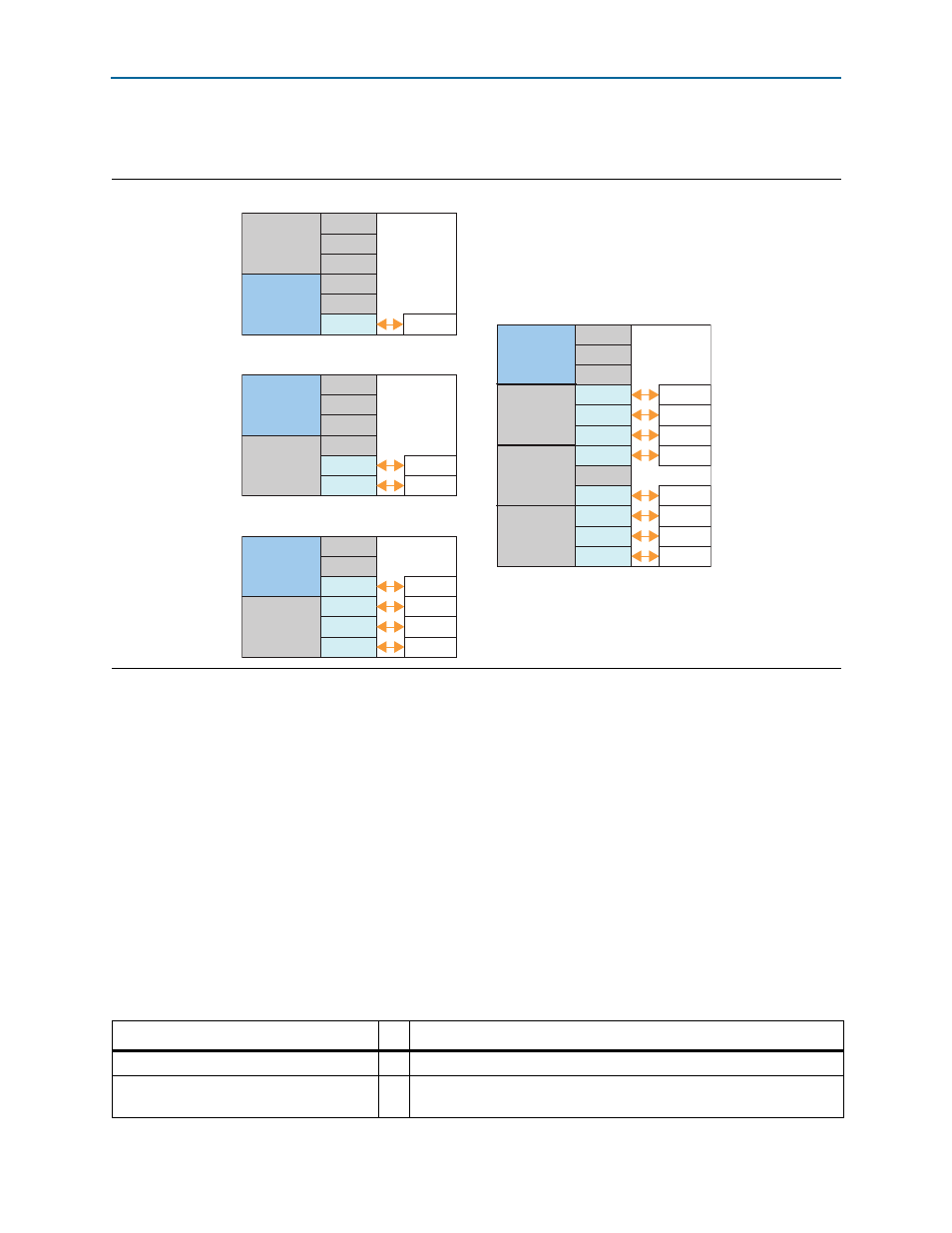

In all figures channels and PLLs that are gray are unused.

PIPE Interface Signals

The PIPE signals are available so that you can simulate using either the one-bit or the

PIPE interface. Simulation is much faster using the PIPE interface. You can use the 8-

bit PIPE interface for simulation even though your actual design includes the serial

interface to the internal transceivers. However, it is not possible to use the Hard IP

PIPE interface in an actual device.

describes the PIPE interface signals used

for a standard 16-bit SDR or 8-bit SDR interface. In

, signals that include

lane number 0 also exist for lanes 1-7. In Qsys, the signals that are part of the PIPE

interface have the prefix, hip_pipe. The signals which are included to simulate the PIPE

interface have the prefix, hip_pipe_sim_pipe.

Figure 7–37. Channel Placement Using ATX PLL

&K

&K

&K

&K

&K

$7;3//

&K

3&,H+DUG,3

$7;3//

&K

&K

&K

&K

&K

&K

$7;3//

&K

$7;3//

3&,H+DUG,3

&K

&K

&K

&K

&K

&K

&K

$7;3//

$7;3//

&K

3&,H+DUG,3

$7;3//

&K

&K

&K

&K

&K

&K

&K

&K

&K

$7;3//

$7;3//

&K

$7;3//

&K

&K

&K

&K

&K

&K

&K

&K

&K

&K

3&,H+DUG,3

&K

&K

&K

&K

[

[

[

[

Table 7–26. PIPE Interface Signals (Part 1 of 4)

Signal I/O

Description

txdata0[7:0]

O

Transmit data

. This bus transmits data on lane

.

txdatak0

O

Transmit data control

. This signal serves as the control bit for

txdata

.