Altera Arria V Hard IP for PCI Express User Manual

Page 134

7–36

Chapter 7: IP Core Interfaces

Arria V Hard IP for PCI Express

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

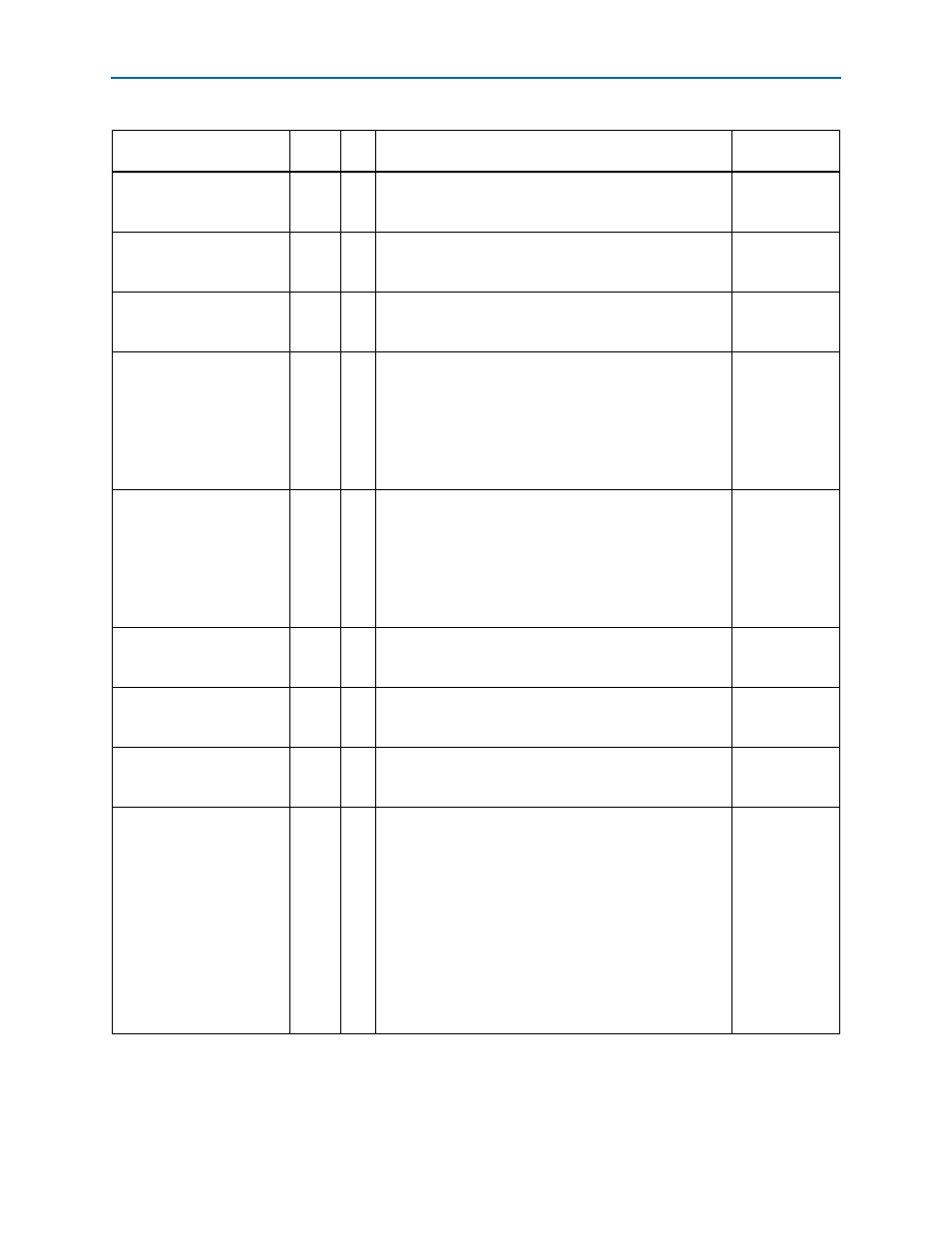

cfg_io_lim

20

O

The upper 20 bits of the IO limit registers of the Type1

Configuration Space. This register is only available in Root

Port mode.

0x01C

cfg_np_bas

12

O

The upper 12 bits of the memory base register of the Type1

Configuration Space. This register is only available in Root

Port mode.

EXP ROM

cfg_np_lim

12

O

The upper 12 bits of the memory limit register of the Type1

Configuration Space. This register is only available in Root

Port mode.

EXP ROM

cfg_pr_bas

44

O

The upper 44 bits of the prefetchable base registers of the

Type1 Configuration Space. This register is only available in

Root Port mode.

0x024 and

Prefetchable

memory

cfg_pr_lim

44

O

The upper 44 bits of the prefetchable limit registers of the

Type1 Configuration Space. Available in Root Port mode.

0x024 and

Prefetchable

memory

cfg_pmcsr

32

O

cfg_pmcsr[31:16]

is Power Management Control and

cfg_pmcsr[15:0]

is the Power Management Status

register.

0x07C

cfg_msix

16

O

MSI-X message control.

0x068

cfg_msi

16

O

MSI message control. Refer to

for the fields of

this register.

0x050

cfg_tcvcmap

24

O

Configuration traffic class (TC)/virtual channel (VC)

mapping. The Application Layer uses this signal to generate

a TLP mapped to the appropriate channel based on the

traffic class of the packet.

cfg_tcvcmap[2:0]

: Mapping for TC0 (always 0).

cfg_tcvcmap[5:3]

: Mapping for TC1.

cfg_tcvcmap[8:6]

: Mapping for TC2.

cfg_tcvcmap[11:9]

: Mapping for TC3.

cfg_tcvcmap[14:12]

: Mapping for TC4.

cfg_tcvcmap[17:15]

: Mapping for TC5.

cfg_tcvcmap[20:18]

: Mapping for TC6.

cfg_tcvcmap[23:21]

: Mapping for TC7.

—

Table 7–14. Configuration Space Register Descriptions (Part 3 of 4)

Register

Width

Dir

Description

Register

Reference