Altera Arria V Hard IP for PCI Express User Manual

Page 241

Chapter 17: Testbench and Design Example

17–19

Root Port Design Example

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

■

Test Driver (altpcietb_bfm_driver_rp.v)—the chaining DMA Endpoint test driver

which configures the Root Port and Endpoint for DMA transfer and checks for the

successful transfer of data. Refer to the

“Test Driver Module” on page 17–14

for a

detailed description.

You can use the example Root Port design for Verilog HDL simulation. All of the

modules necessary to implement the example design with the variation file are

contained in altpcietb_bfm_ep_example_chaining_pipen1b.v.

The top-level of the testbench instantiates the following key files:

■

altlpcietb_bfm_top_ep.v

— this is the Endpoint BFM. This file also instantiates the

SERDES and PIPE interface.

■

altpcietb_pipe_phy.v

—used to simulate the PIPE interface.

■

altpcietb_bfm_ep_example_chaining_pipen1b.v

—the top-level of the Root Port

design example that you use for simulation. This module instantiates the Root Port

variation,

altpcietb_bfm_vc_intf

_

serial interfaces for the simulation environment. This module has two debug ports

named

test_out

_

icm

(which is the

test_out

signal from the Hard IP) and

test_in

which allows you to monitor and control internal states of the Hard IP

variation. (Refer to

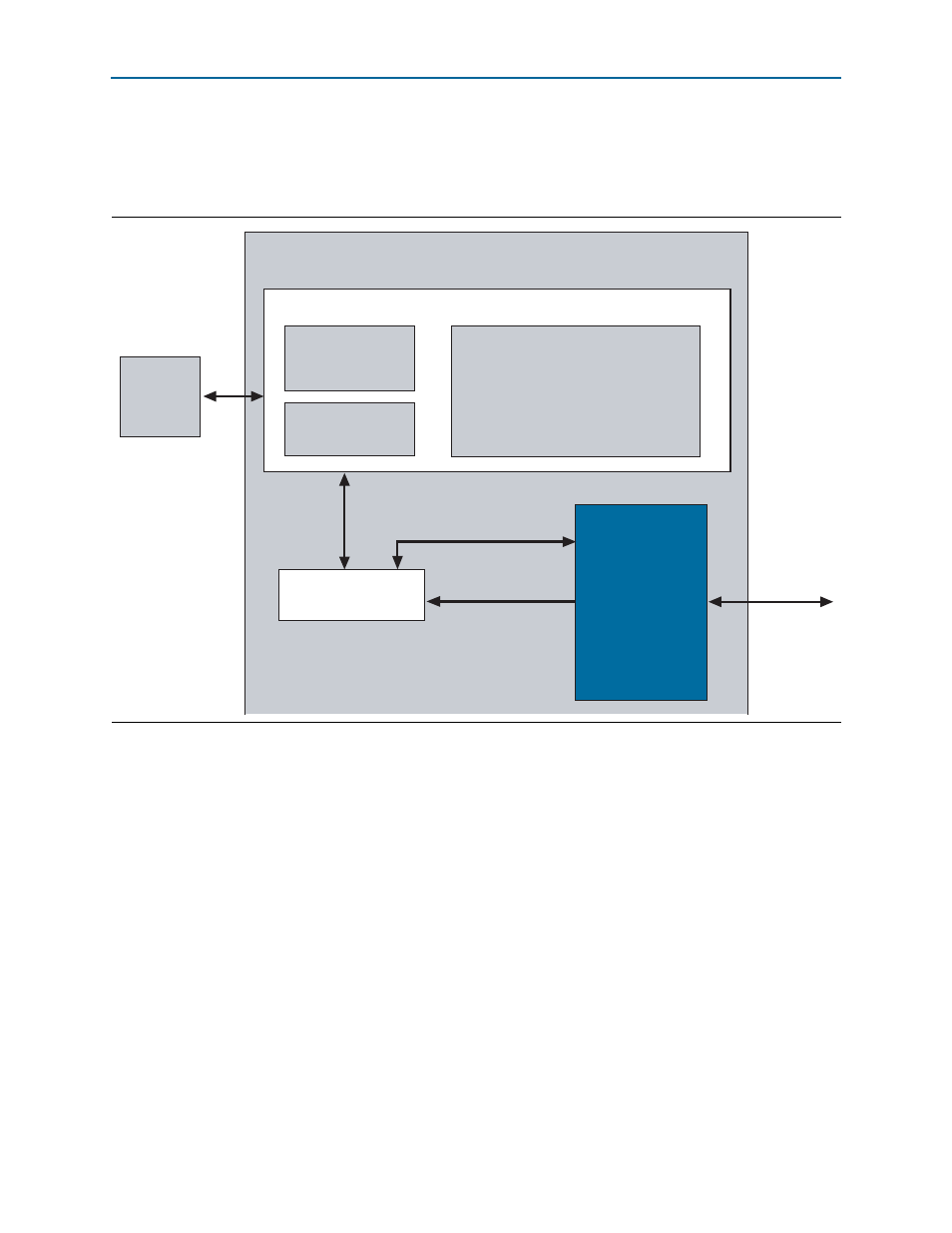

Figure 17–3. Root Port Design Example

Root Port

Variation

(variation_name.v)

Avalon-ST Interface

(altpcietb_bfm_vc_intf)

Test Driver

(altpcietb_bfm_

driver_rp.v)

BFM Shared Memory

(altpcietb_bfm_shmem

_common)

BFM Read/Write Shared Request Procedures

BFM Configuration Procedures

BFM Request Interface

(altpcietb_bfm_req_intf_common)

BFM Log Interface

(altpcietb_bfm_log

_common)

PCI Express

Link

Root Port BFM Tasks and Shared Memory

altpcietb_bfm_ep_example_chaining_pipe1b.v

Avalon-ST