Ip core verification, Performance and resource utilization – Altera Arria V Hard IP for PCI Express User Manual

Page 14

1–6

Chapter 1: Datasheet

IP Core Verification

Arria V Hard IP for PCI Express

December 2013

Altera Corporation

User Guide

IP Core Verification

To ensure compliance with the PCI Express specification, Altera performs extensive

validation of the Arria V Hard IP Core for PCI Express. The Gen1 ×8 and Gen2 ×4

Endpoints were certified PCI Express compliant at PCI-SIG Compliance Workshop

#79 in February 2012.

The simulation environment uses multiple testbenches that consist of

industry-standard BFMs driving the PCI Express link interface. A custom BFM

connects to the application-side interface.

Altera performs the following tests in the simulation environment:

■

Directed and pseudo random stimuli areArria V applied to test the Application

Layer interface, Configuration Space, and all types and sizes of TLPs.

■

Error injection tests that inject errors in the link, TLPs, and Data Link Layer

Packets (DLLPs), and check for the proper responses

■

PCI-SIG

®

Compliance Checklist tests that specifically test the items in the checklist

■

Random tests that test a wide range of traffic patterns

Performance and Resource Utilization

Because the Arria V Hard IP for PCI Express IP core is implemented in hardened

logic, it uses less than 1% of Arria V resources. The Avalon-MM Arria V Hard IP for

PCI Express includes a bridge implemented in soft logic.

Table 1–4

shows the typical

expected device resource utilization for selected configurations of the Avalon-MM

Arria V Hard IP for PCI Express using the current version of the Quartus II software

targeting a Arria V (5AGXFB3H6F35C6ES) device. With the exception of M10K

memory blocks, the numbers of ALMs and logic registers in

Table 1–4

are rounded up

to the nearest 100. Resource utilization numbers reflect changes to the resource

utilization reporting starting in the Quartus II software v12.1 release 28 nm device

families and upcoming device families.

f

For information about Quartus II resource utilization reporting, refer to

in the Quartus II Help.

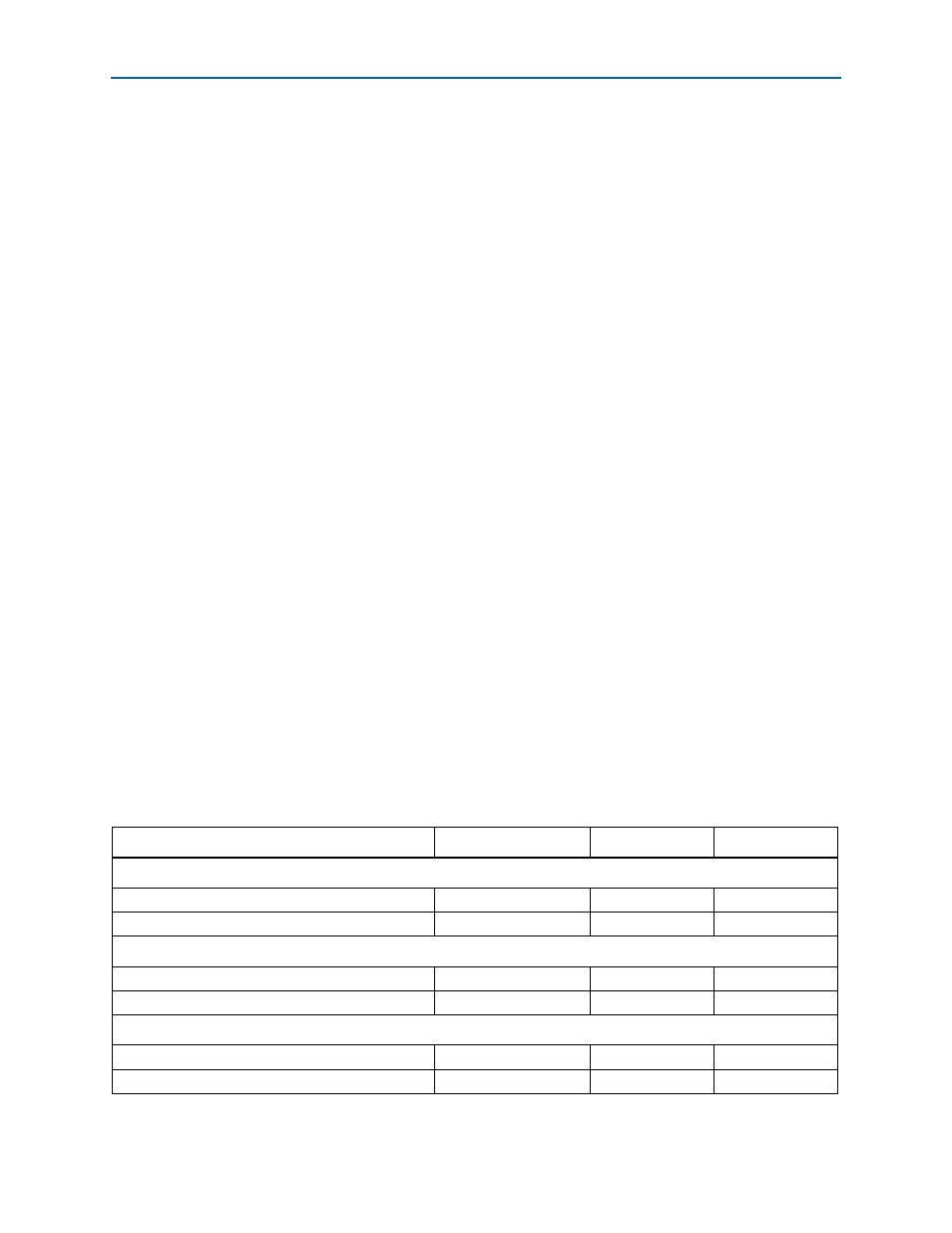

Table 1–5. Performance and Resource Utilization (Part 1 of 2)

ALMs

Memory M10K

Logic Registers

Avalon-MM Bridge

Gen1 ×4

1250

27

1700

Gen2 ×8

2100

35

3050

Avalon-MM Interface–Burst Capable Requester/Single DWord Completer

64

1150

23

1700

128

1600

29

2550

Avalon-MM Interface-Burst Capable Completer Only

64

600

11

900

128

1350

22

2300